zilog

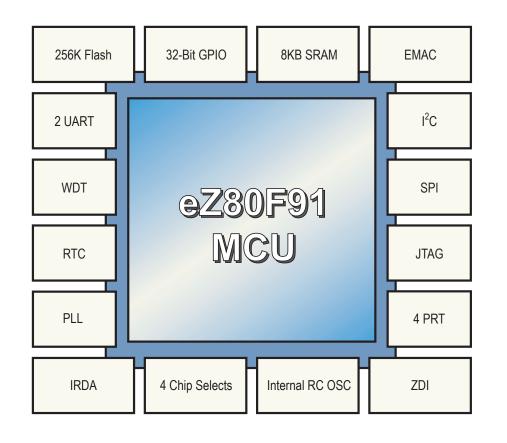

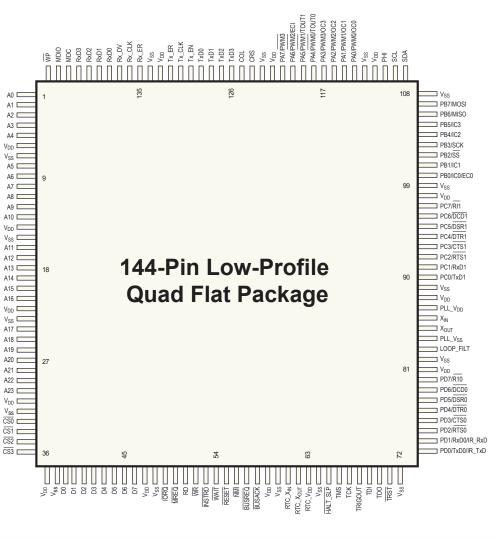

## azaof91 MCU Easy Reference Chart

|                | A1 ball pad corner |   | 12               | 11              | 10               | 9               | 8               | 7                       | 6               | 5               | 4               | 3               | 2               |   |

|----------------|--------------------|---|------------------|-----------------|------------------|-----------------|-----------------|-------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|---|

| 12 11 10 9 8 7 | 654321             | А | SDA              | SCL             | PA0              | PA4             | PA7             | COL                     | TxD0            | V <sub>DD</sub> | Rx_DV           | MDC             | WPn             | A |

| <b>A</b>       | 000000             | В | V <sub>ss</sub>  | PHI             | PA1              | PA3             | V <sub>DD</sub> | TxD3                    | Tx_EN           | V <sub>ss</sub> | RxD1            | MDIO            | A2              |   |

| 000000         | 000000             | c | PB6              | PB7             |                  | PA5             |                 | TxD2                    | Tx_CLK          | Rx_CLK          | RxD3            | A3              |                 |   |

| 0 0 0 0 0 0    | 000000             | C | FDU              | FD/             | V <sub>DD</sub>  | FAU             | V <sub>ss</sub> | TXDZ                    | TX_OLK          | KX_OLK          | KXD3            | AJ              | V <sub>ss</sub> | V |

| 000000         | 000000             | D | PB1              | PB3             | PB5              | V <sub>ss</sub> | CRS             | TxD1                    | Rx_ER           | RxD2            | A4              | A8              | A6              |   |

| 000000         | 000000             | E | PC7              | $V_{DD}$        | PB0              | PB4             | PA2             | Tx_ER                   | RxD0            | A5              | A11             | V <sub>ss</sub> | $V_{DD}$        | A |

| 000000         | 000000             | F | PC3              | PC4             | PC5              | V <sub>ss</sub> | PB2             | PA6                     | A9              | A17             | A15             | A14             | A13             | A |

| 00000          | 000000             | G | V <sub>ss</sub>  | PC0             | PC1              | PC2             | PC6             | PLL_V <sub>SS</sub>     | V <sub>ss</sub> | A23             | A20             | V <sub>ss</sub> | $V_{DD}$        | A |

| • 000000       | 000000             | н | X <sub>OUT</sub> | $X_{IN}$        | $PLL_V_{DD}$     | V <sub>DD</sub> | PD7             | TMS                     | V <sub>ss</sub> | D5              | V <sub>SS</sub> | A21             | A19             | A |

| 000000         | 000000             | J | V <sub>SS</sub>  | V <sub>DD</sub> | LOOP<br>FILT_OUT | PD4             | TRIGOUT         | RTC_<br>V <sub>DD</sub> | NMIn            | WRn             | D2              | CS0n            | V <sub>DD</sub> | 1 |

| 000000         | 000000             | к | PD5              | PD6             | PD3              | TDI             | V <sub>SS</sub> | V <sub>DD</sub>         | RESETn          | RDn             | V <sub>DD</sub> | D1              | CS2n            | С |

| 000000         | 000000             | L | PD1              | PD2             | TRSTn            | TCK             | RTC_<br>XOUT    | BUSACKn                 | WAITn           | MREQn           | D6              | D4              | D0              | ( |

| 1 0 0 0 0 0 0  |                    | м | PD0              | V <sub>SS</sub> | TDO              | HALT_<br>SLPn   | RTC_<br>XIN     | BUSREQn                 | INSTRDn         | IORQn           | D7              | D3              | V <sub>SS</sub> | , |

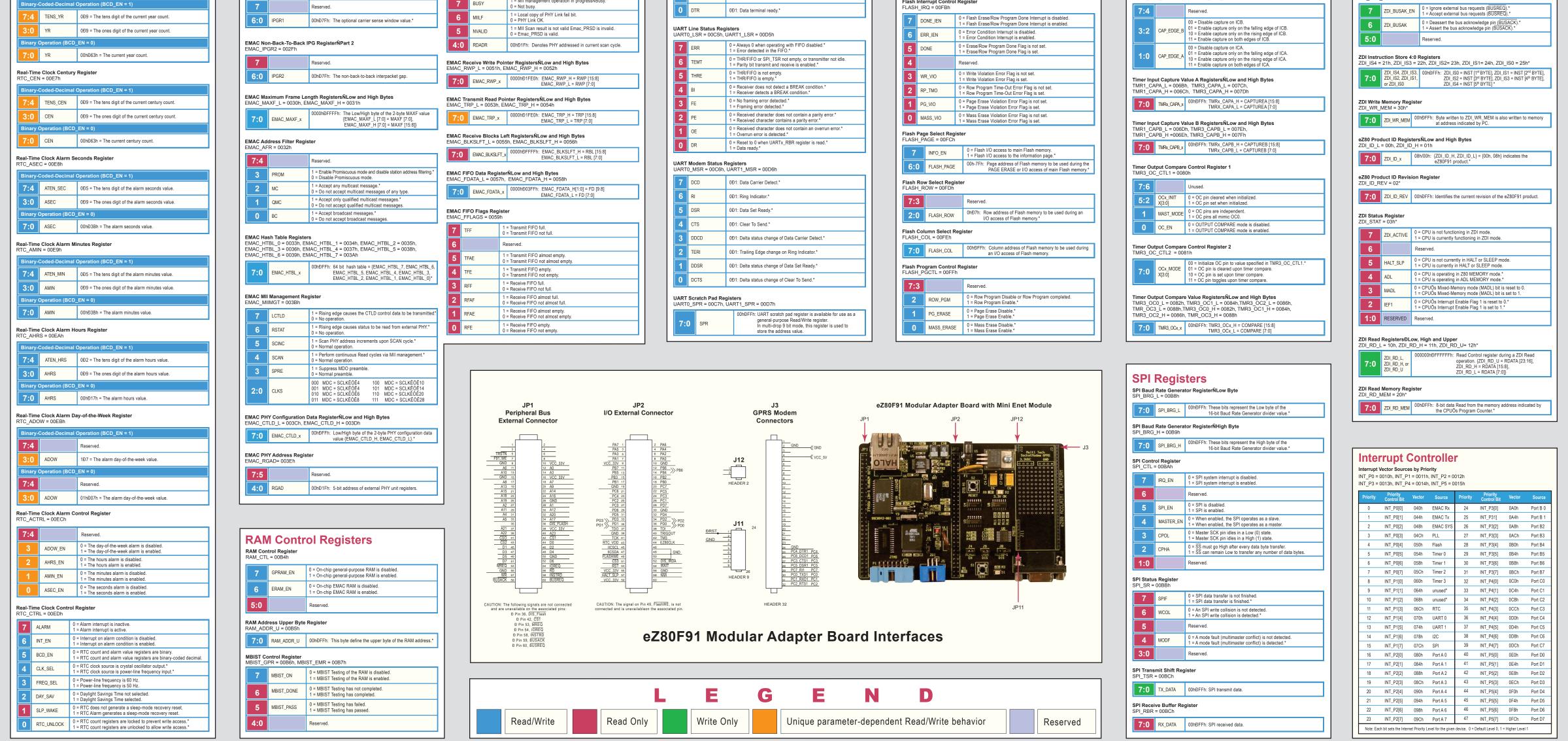

| hip Select Registers                                                                                                                                                                                          | GPIO Registers       Port x Alternate Registers 2<br>PA_ALT2 = 0099h, PB_ALT2 = 0090h, PB_ALT2 = 0000h, P                                 | Clock Perinheral Power-Down Register 1                                                                                                                                                 | Watch-Dog Timer Registers<br>Watch-Dog Timer Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I <sup>2</sup> C Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IrDA Registers                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lect x Lower Bound Register<br>R = 00A8h, CS1_LBR = 00ABh, CS2_LBR = 00AEh, CS3_LBR = 00B1h                                                                                                                   | GPIO         PX_ALT2         PX_ALT1         PX_DR         PA_ALT1 = 0098h, PB_ALT1 = 009Ch, P           GPIO         PX_ALT2         PX_DR         PA_ALT1 = 0098h, PB_ALT1 = 009Ch, P           Mode         Bits [7:0]         Bits [7:0]         Port Mode         PA_ALT0 = 00A7h, P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ALT1 = 00A0h, PD_ALT1 = 00A4h CLK_PPD1 = 00DBh                                                                                                                                         | WDT_CTL = 0093h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I2C_SAR = 00C8h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Infrared Encoder/Decoder Control Register<br>IR_CTL = 00BFh                                                                                                                                         |

| CSx_LBR 0 = Lower bound of the Memory Chip Select address range.*<br>1 = Address value of the I/O Chip Select.*                                                                                               | 1         0         0         Output         0         Port x Data Direction Registers         PA_DDR = 0097h, PB_DDR = 0098h, P0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DDR = 009Fh, PD_DDR = 00A3h     7     GPI0_D_OFF     0     0 System clock to GPI0 Port D is powered up.                                                                                | 7     WDT_EN     0 = WDT is disabled.       1 = WDT is enabled.*     0 = WDT is enabled.*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7:1 SLA 00hD7Fh: 7-bit slave address or upper 2 bits of address when operating in 10-bit mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7:3 Reserved.                                                                                                                                                                                       |

| ct x Upper Bound Register                                                                                                                                                                                     | 0         0         1         Output         1         Port x Data Registers           2         0         0         1         0         Input from pin         High impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                        | 6 NMLOUT 1 = WDT time-but resets the 2200 CPU.<br>9 = WDT time-but generates a NMI to the CPU.<br>0 = RESET caused by external full-chip reset or ZDI reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 = I <sup>2</sup> C not enabled to recognize the General Call Address.<br>1 = I <sup>2</sup> C enabled to recognize the General Call Address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2 LOOP_BACK 0 = Internal LOOPBACK mode is disabled.<br>1 = Internal LOOPBACK mode is enabled.*                                                                                                      |

| = 00A9h, CS1_UBR = 00AC, CS2_UBR = 00AFh, CS3_UBR = 00B2h                                                                                                                                                     | 0         0         1         Input from pin         High impedance         PX_ALT2         PX_ALT1         PX           3         0         1         0         Open-drain output         0         7         Mode for PX7, where x = Port A,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 = System clock to GPIO Port B is powered up.                                                                                                                                         | KSI_FLAG     1 = RESET caused by WDT time-out.*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I <sup>2</sup> C Extended Slave Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 IR_RXEN 0 = IR_RXD data is ignored.<br>1 = IR_RXD data is passed to the UART0 RxD.                                                                                                                |

| CSx_UBR 0 = Upper bound of the Memory Chip Select address range.*<br>1 = No effect.                                                                                                                           | 0         1         0         1         Open-drain I/O         High impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C. or D.                                                                                                                                                                               | 4 NMI_FLAG 1 = NMI caused by WDT time-out.*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I2C_XSAR = 00C9h           7.0         SLAX           00hDFFh: Least significant 8 bits of the 10-bit extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 = Infrared Encoder/Decoder is disabled.                                                                                                                                                           |

| ct x Control Register<br>= 00AAh, CS1_CTL = 00ADh, CS2_CTL = 00B0h, CS3_CTL = 00B3h                                                                                                                           | 0 1 1 1 0pen-source output 1<br>5 1 0 0 0 Reserved High impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        | 3:2 WDT_CLK 01 = WDT clock source is Real-Time Clock source*.<br>10 = WDT clock source is internal RC oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | slave address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 = Infrared Encoder/Decoder is enabled.                                                                                                                                                            |

| 000 = 0 wait states are asserted when this chip select is active.<br>001 = 1 wait state is asserted when this chip select is active.                                                                          | 6 1 0 0 1 InterruptiNdual edge triggered High impedance 4 Mode for Px4, where x = Port A,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | i = System clock to FC is powered up.                                                                                                                                                  | 00 = WDT time-out period is 2 <sup>27</sup> clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I <sup>2</sup> C Data Register<br>I2C_DR = 00CAh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                     |

| 010 = 2 wait states are asserted when this chip select is active.<br>011 = 3 wait states are asserted when this chip select is active.                                                                        | 7         1         0         1         0         Pott B, C, or DNalternative function controls port I/O         3         Mode for Px3, where x = Port A,           1         0         1         1         Port B, C, or DNalternative function controls port I/O         3         Mode for Px3, where x = Port A,           2         Mode for Px2, where x = Port A,         4         0         0         Intervalue function controls port I/O         2         Mode for Px2, where x = Port A,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 = System clock to UART1 is powered up.                                                                                                                                               | <b>1:0</b> WDT_PERIOD 10 F WDT lime-out period is 2 <sup>22</sup> clock cycles.<br>11 = WDT time-out period is 2 <sup>18</sup> clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7:0 DATA 00hDFFh: I <sup>2</sup> C data byte.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                     |

| 100 = 4 wait states are asserted when this chip select is active.     101 = 5 wait states are asserted when this chip select is active.     110 = 6 wait states are asserted when this chip select is active. | 8         1         1         0         0         InterruptNactive Low         High impedance           1         1         0         1         InterruptNactive High         High impedance         1         Mode for Px2, where x = Port A,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 UART0_OFF 1 = System clock to UART0 is powered up                                                                                                                                    | Watch-Dog Timer Reset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I <sup>2</sup> C Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Multi-PWM Control Registers                                                                                                                                                                         |