# S3 Family 8-Bit Microcontrollers

# S3F8S19A

# **Product Specification**

PS039001-0616

PRELIMINARY

Copyright ©2016 Zilog<sup>®</sup>, Inc. All rights reserved. www.zilog.com

## Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

## LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2016 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

S3 and Z8 are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

iii

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Description           | Page |

|-------------|-------------------|-----------------------|------|

| Jun<br>2016 | 01                | Original Zilog issue. | All  |

# **Chip Handling Guide**

#### **Precaution against Electrostatic Discharge**

When using semiconductor devices, ensure that the environment is protected against static electricity:

- 1. Wear antistatic clothes and use earth band.

- 2. All objects that are in direct contact with devices must be made up of materials that do not produce static electricity.

- 3. Ensure that the equipment and work table are earthed.

- 4. Use ionizer to remove electron charge.

#### Contamination

Do not use semiconductor products in an environment exposed to dust or dirt adhesion.

#### **Temperature/Humidity**

Semiconductor devices are sensitive to:

- Environment

- Temperature

- Humidity

High temperature or humidity deteriorates the characteristics of semiconductor devices. Therefore, do not store or use semiconductor devices in such conditions.

#### **Mechanical Shock**

Do not to apply excessive mechanical shock or force on semiconductor devices.

#### Chemical

Do not expose semiconductor devices to chemicals because exposure to chemicals leads to reactions that deteriorate the characteristics of the devices.

#### **Light Protection**

In non- Epoxy Molding Compound (EMC) package, do not expose semiconductor IC to bright light. Exposure to bright light causes malfunctioning of the devices. However, a few special products that utilize light or with security functions are exempted from this guide.

#### Radioactive, Cosmic and X-ray

Radioactive substances, cosmic ray, or X-ray may influence semiconductor devices. These substances or rays may cause a soft error during a device operation. Therefore, ensure to shield the semiconductor devices under environment that may be exposed to radioactive substances, cosmic ray, or X-ray.

#### EMS (Electromagnetic Susceptibility)

Strong electromagnetic wave or magnetic field may affect the characteristic of semiconductor devices during the operation under insufficient PCB circuit design for Electromagnetic Susceptibility (EMS).

# **Table of Contents**

| Chip Handling Guide                                                   | iv  |

|-----------------------------------------------------------------------|-----|

| Table of Contents                                                     | v   |

| List of Figures                                                       | xv  |

| List of Tables                                                        | xix |

| List of Examples                                                      | xxi |

| 1 Product Overview                                                    |     |

| 1.1 S3C8 Series Microcontrollers                                      |     |

| 1.2 S3F8S19A Microcontroller                                          |     |

| 1.3 Features                                                          |     |

| 1.3.1 CPU                                                             |     |

| 1.3.2 Memory                                                          |     |

| 1.3.3 Instruction Set                                                 |     |

| 1.3.4 I/O Pins                                                        |     |

| 1.3.5 Interrupts                                                      | 1-2 |

| 1.3.6 Timers and Timer/Counters                                       | 1-3 |

| 1.3.7 Watch Timer                                                     |     |

| 1.3.8 Analog to Digital Converter                                     | 1-3 |

| 1.3.9 Two Channels Universal Asynchronous Receiver/Transmitter (UART) | 1-3 |

| 1.3.10 Multi-Master I2C Bus                                           |     |

| 1.3.11 SPI                                                            |     |

| 1.3.12 LCD Controller/Driver                                          |     |

| 1.3.13 Two Power-Down Modes                                           |     |

| 1.3.14 Oscillation Sources                                            |     |

| 1.3.15 Instruction Execution Time                                     |     |

| 1.3.16 Built-In RESET Circuit (LVR)                                   |     |

| 1.3.17 Low Voltage Detect Circuit (LVD)                               |     |

| 1.3.18 Operating Voltage Range                                        |     |

| 1.3.19 Package Type<br>1.3.20 Operating Temperature Range             |     |

| 1.3.20 Operating Temperature Range<br>1.3.21 Smart Option             |     |

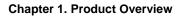

| 1.4 Block Diagram                                                     |     |

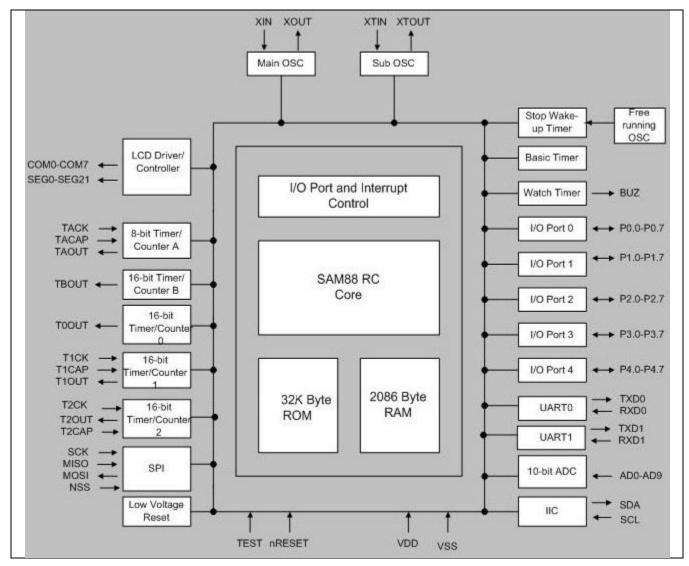

| 1.5 Pin Assignments                                                   |     |

| 1.6 Pin Descriptions                                                  |     |

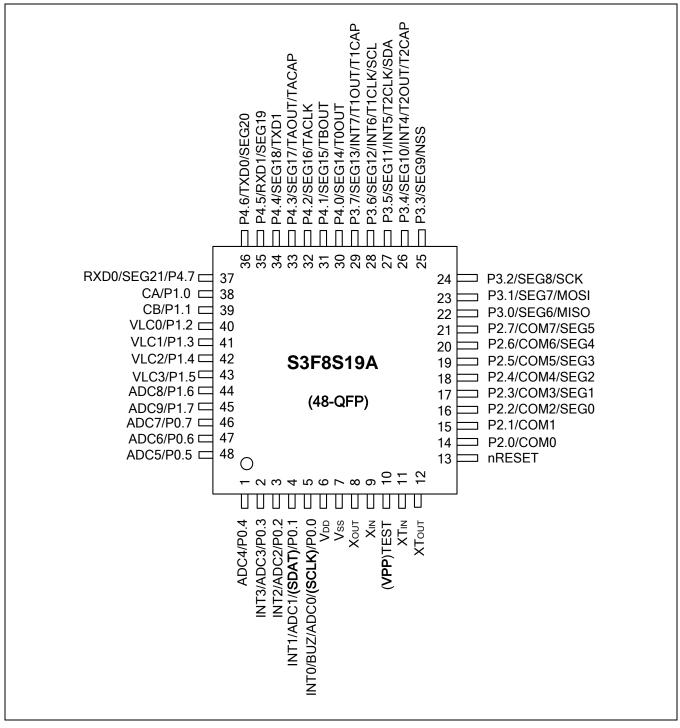

| 1.7 Pin Circuits                                                      |     |

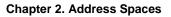

| 2 Address Spaces                                                      | 2-1 |

| 2.1 Overview                                                          | 2-1 |

| 2.2 Program Memory                                                    |     |

| 2.3 Smart Option                                                      |     |

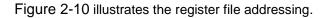

| 2.4 Register Architecture                                             |     |

| 2.5 Register Page Pointer                                             |     |

| 2.6 Register Set 1                                                          |      |

|-----------------------------------------------------------------------------|------|

| 2.7 Register Set 2                                                          |      |

| 2.8 Prime Register Space                                                    |      |

| 2.9 Working Registers                                                       |      |

| 2.10 Using the Register Points                                              |      |

| 2.11 Register Addressing                                                    |      |

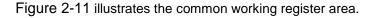

| 2.12 Common Working Register Area (C0H–CFH)                                 |      |

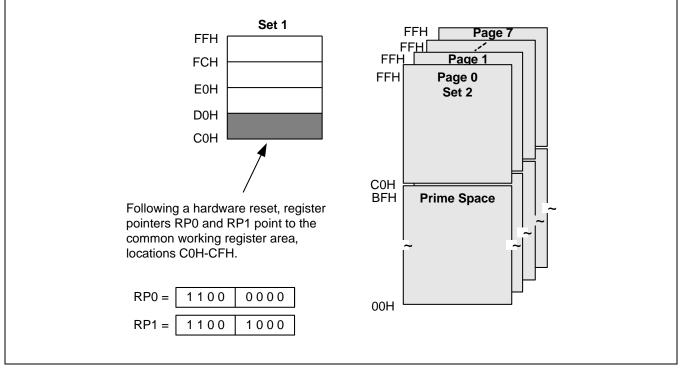

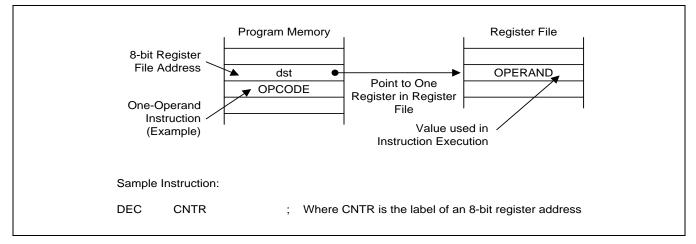

| 2.13 4-Bit Working Register Addressing                                      |      |

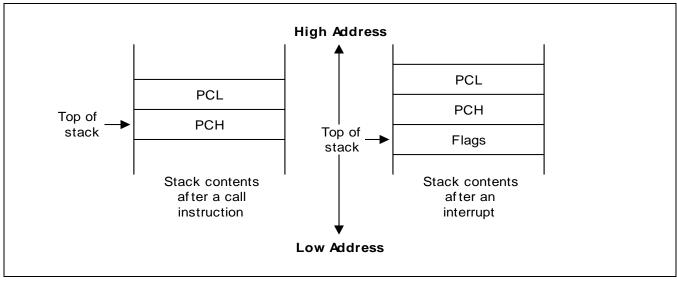

| 2.14 8-Bit Working Register Addressing                                      |      |

| 2.15 System and User Stack                                                  |      |

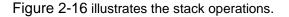

| 2.15.1 Stack Operations                                                     |      |

| 2.15.2 User-Defined Stacks<br>2.15.3 Stack Pointers (SPL, SPH)              |      |

|                                                                             |      |

| 3 Addressing Modes                                                          |      |

| 3.1 Overview                                                                |      |

| 3.2 Register Addressing Mode                                                |      |

| 3.3 Indirect Register Addressing Mode                                       |      |

| 3.4 Indexed Addressing Mode                                                 | 3-6  |

| 3.5 Direct Address Mode                                                     |      |

| 3.6 Indirect Address Mode                                                   |      |

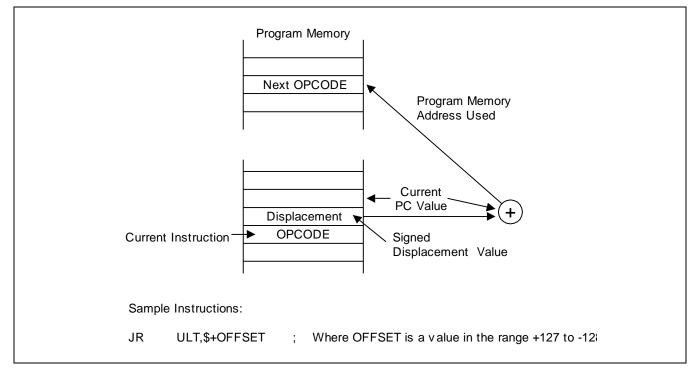

| 3.7 Relative Address Mode                                                   |      |

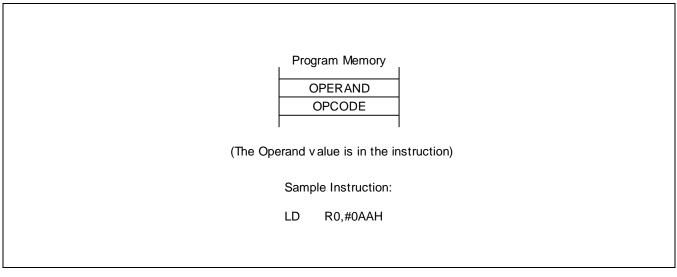

| 3.8 Immediate Mode                                                          |      |

| 4 Control Registers                                                         | 4-1  |

| 4.1 Overview                                                                |      |

| 4.1.1 ADCON-A/D Converter Control Register (D2H, SET1)                      |      |

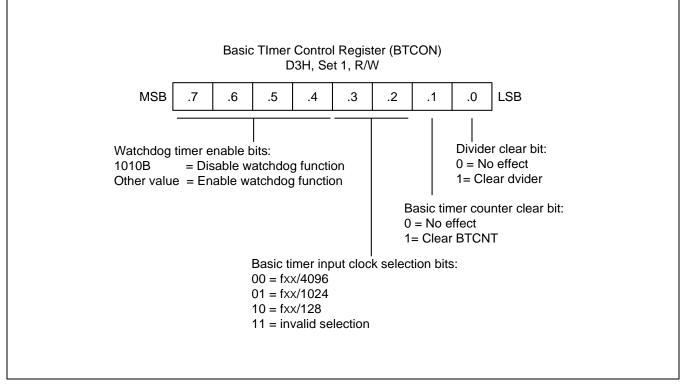

| 4.1.2 BTCON-Basic Timer Control Register (D3H, SET1)                        |      |

| 4.1.3 CLKCON-Clock Control Register (D4H, SET1)                             |      |

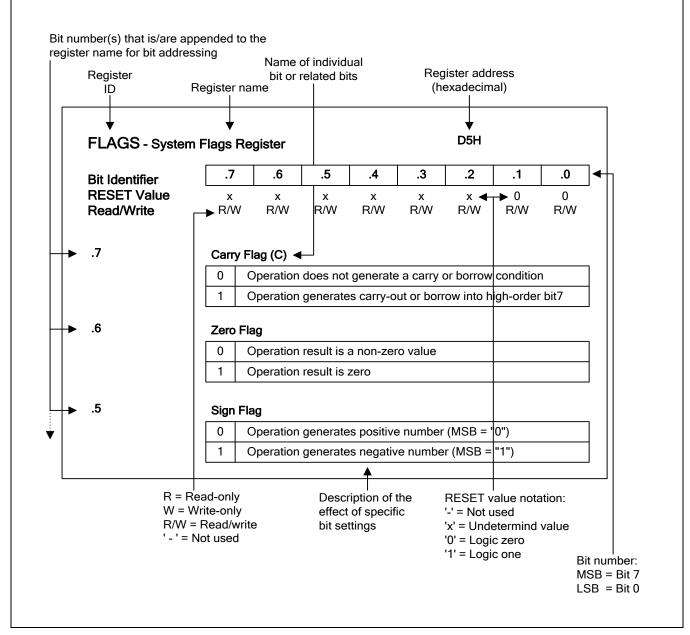

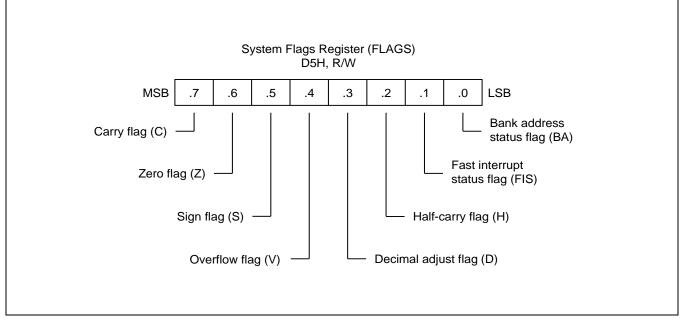

| 4.1.4 FLAGS-System Flags Register (D5H, SET1)                               |      |

| 4.1.5 FMCON-Flash Memory Control Register (0BH, Page 8)                     |      |

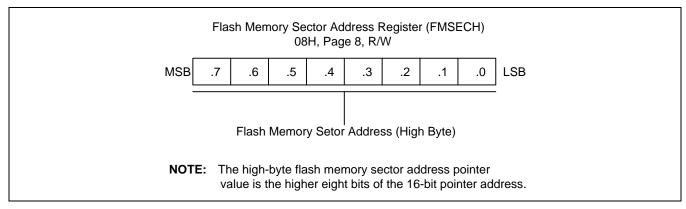

| 4.1.6 FMSECH-Flash Memory Sector Address Register (High Byte) (08H, Page 8) | 4-13 |

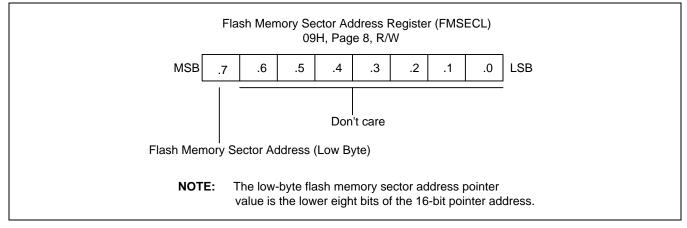

| 4.1.7 FMSECL-Flash Memory Sector Address Register (Low Byte) (09H, Page 8)  | 4-13 |

| 4.1.8 FMUSR-Flash Memory User Programming Enable Register (0AH, Page 8)     | 4-13 |

| 4.1.9 ICCR-Multi-Master I2C Bus Clock Control Register (0CH, PAGE8)         |      |

| 4.1.10 ICSR-I2C Status Register (0DH, PAGE 8)                               | 4-15 |

| 4.1.11 IMR-Interrupt Mask Register (DDH, SET1)                              |      |

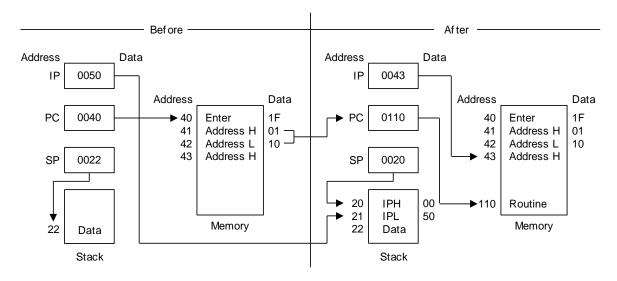

| 4.1.12 IPH-Instruction Pointer (High Byte) (DAH, SET1)                      |      |

| 4.1.13 IPL-Instruction Pointer (Low Byte) (DBH, SET1)                       | 4-17 |

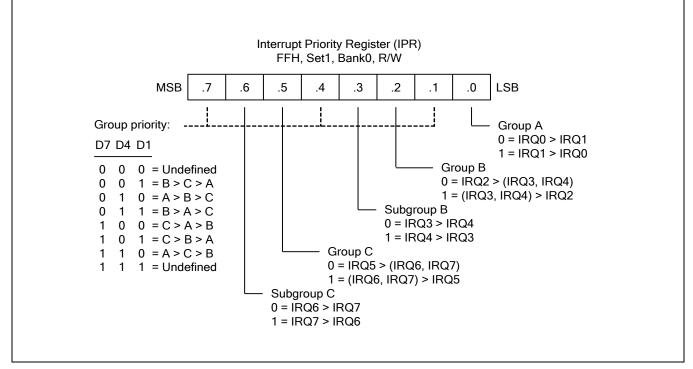

| 4.1.14 IPR-Interrupt Priority Register (FFH, BANK0)                         |      |

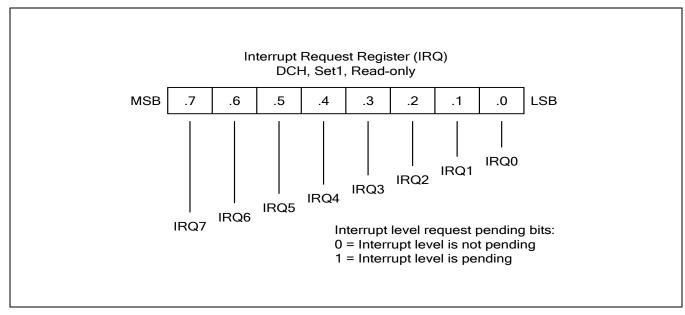

| 4.1.15 IRQ-Interrupt Request Register (DCH, SET1)                           |      |

| 4.1.16 LCON-LCD Control Register (FDH, BANK1)                               | 4-20 |

| 4.1.17 LMOD-LCD Mode Control Register (FCH, BANK1)                          |      |

| 4.1.18 LVDCON-Low Voltage Detector Control Register (FEH, BANK 1)           |      |

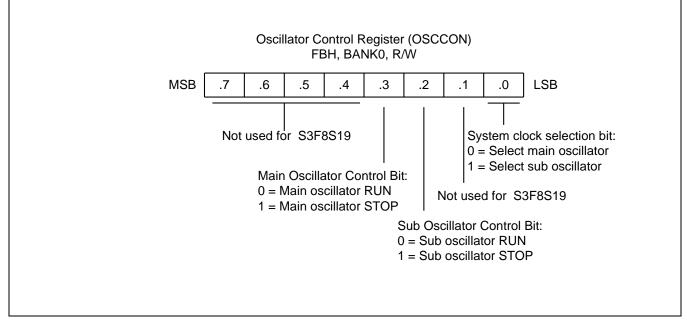

| 4.1.19 OSCCON-Oscillator Control Register (FBH, BANK0)                      |      |

| 4.1.20 OSCCALCON-Internal OSC Calibration Control Register (18H, PAGE8)     |      |

| 4.1.21 P0CONH-Port 0 Control Register High Byte (E0H, BANK1)                |      |

| 4.1.22 P0CONL-Port 0 Control Register Low Byte (E1H, BANK1)                 |      |

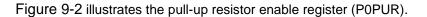

| 4.1.23 POPUR-Port 0 Pull-Up Resistor Enable Register (E2H, BANK1)           |      |

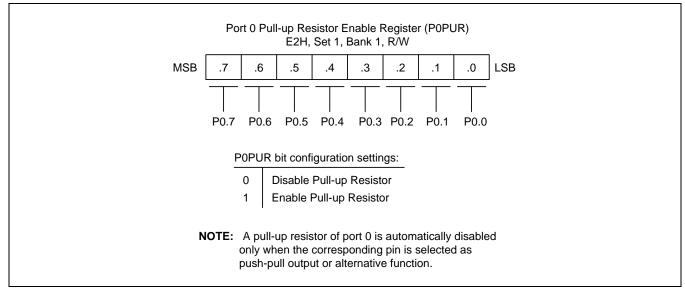

| 4.1.24 POINT-Port 0 Interrupt Control Register (E3H, BANK1)                 |      |

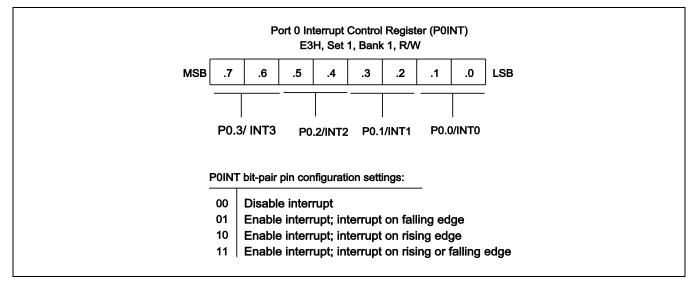

| 4.1.25 P1CONH-Port 1 Control Register High Byte (E4H, BANK1)                | 4-28 |

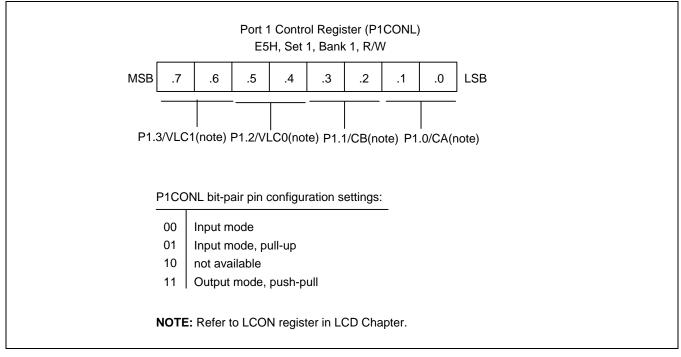

| 4.1.26 P1CONL-Port 1 Control Register Low Byte (E5H, BANK1)                                                                       |     |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

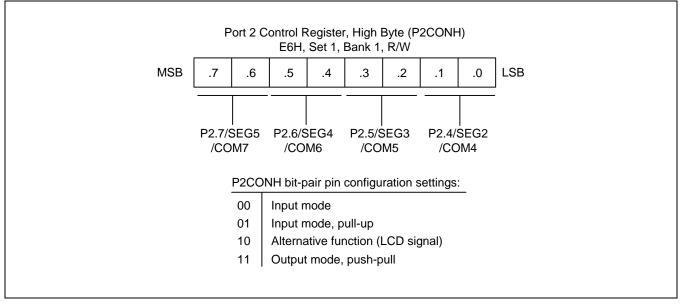

| 4.1.27 P2CONH-Port 2 Control Register High Byte (E6H, BANK1)                                                                      |     |

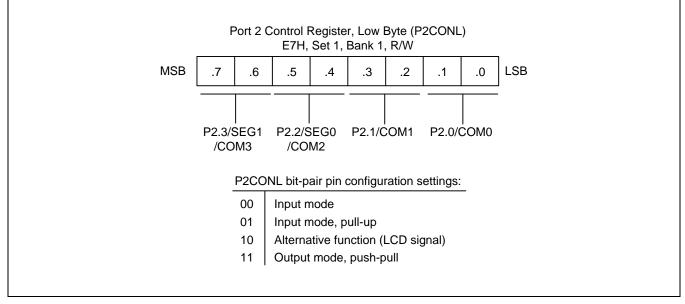

| 4.1.28 P2CONL-Port 2 Control Register Low Byte (E7H, BANK1)                                                                       |     |

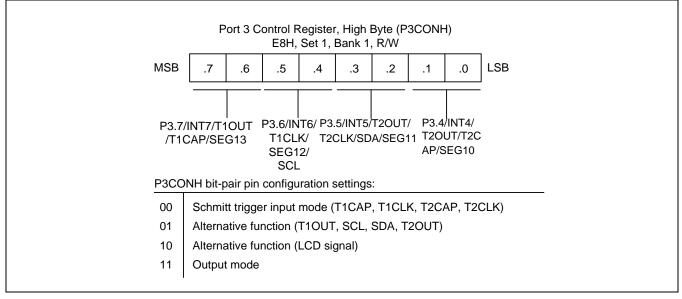

| 4.1.29 P3CONH-Port 3 Control Register High Byte (E6H, BANK1)                                                                      |     |

| 4.1.30 P3CONL-Port 3 Control Register Low Byte (E9H, BANK1)                                                                       |     |

| 4.1.31 P3INT-Port 3 Interrupt Control Register (EBH, BANK1)                                                                       |     |

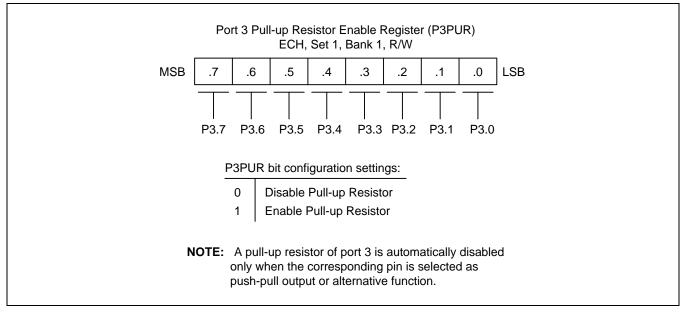

| 4.1.32 P3PUR-Port 3 Pull-Up Resistor Enable Register (ECH, BANK1)                                                                 |     |

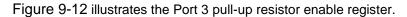

| 4.1.33 P4CONH-Port 4 Control Register High Byte (EEH, BANK1)                                                                      |     |

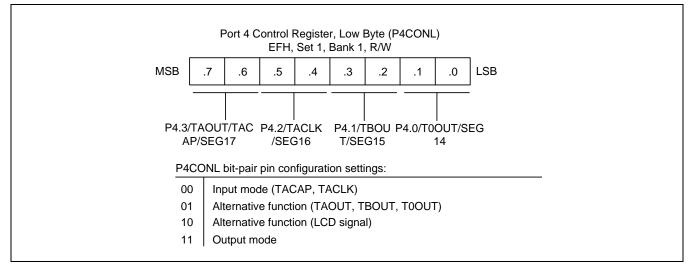

| 4.1.34 P4CONL-Port 4 Control Register Low Byte (EFH, BANK1)                                                                       |     |

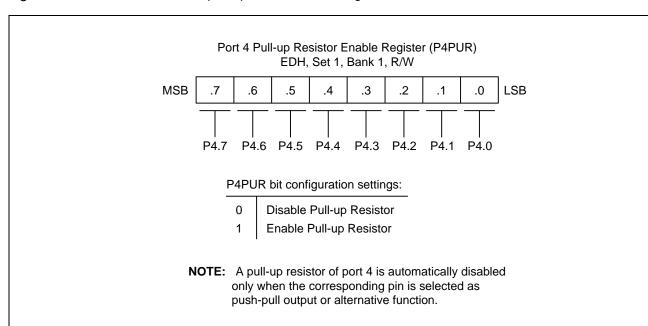

| 4.1.35 P4PUR-Port 4 Pull-Up Resistor Enable Register (EDH, BANK1)                                                                 |     |

| 4.1.36 PNE3-Port 3 N-Channel Open-Drain Mode Register (EAH, BANK1)                                                                |     |

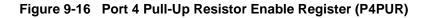

| 4.1.37 PNE4-Port 4 N-Channel Open-Drain Mode Register (F0H, BANK1)                                                                |     |

| 4.1.38 PINTPND-Interrupt Pending Register (F6H, BANK1)                                                                            |     |

| 4.1.39 PP-Register Page Pointer (DFH, SET1)                                                                                       |     |

| 4.1.40 RESETID-Reset Source Indicating Register (FAH, BANK1)                                                                      |     |

| 4.1.41 ROSCCON-Ring Oscillator Control Register (FFH, BANK1)                                                                      |     |

| 4.1.42 RP0-Register Pointer 0 (D6H, SET1)                                                                                         |     |

| 4.1.43 RP1-Register Pointer 1 (D7H, SET1)                                                                                         |     |

| 4.1.44 SPH-Stack Pointer High Byte (D8H, SET1)                                                                                    |     |

| 4.1.45 SPL-Stack Pointer Low Byte (D9H, SET1)                                                                                     |     |

| 4.1.46 SPICON-SPI Control Register (F7H, BANK1)                                                                                   |     |

| 4.1.47 SPISTAT-SPI Status Register (F8H, BANK1)                                                                                   |     |

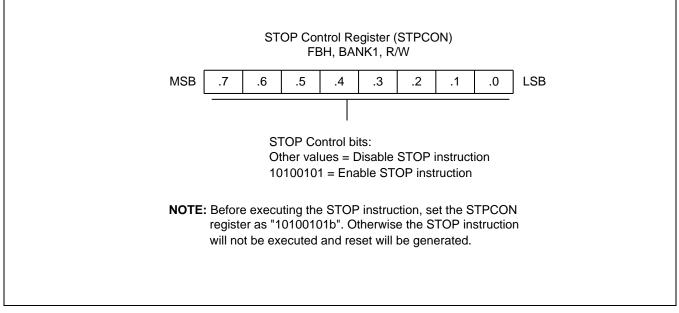

| 4.1.48 STPCON-Stop Mode Control Register (FBH, BANK1)                                                                             |     |

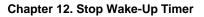

| 4.1.49 SWTCON-Stop Wake-Up Timer Control Register (10H, PAGE8)                                                                    |     |

| 4.1.50 SYM-System Mode Register (DEH, SET1)                                                                                       |     |

| 4.1.51 TACON-Timer A Control Register (E2H, BANK0)                                                                                |     |

| 4.1.52 TAPS-TA Prescaler Register (E3H, BANK0)                                                                                    |     |

| 4.1.53 TBCON-Timer B Control Register (11H, PAGE8)                                                                                |     |

| 4.1.54 TBTRG-Timer B Trigger Control Register (16H, Page 8)                                                                       |     |

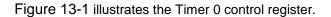

| 4.1.55 T0CON-Timer 0 Control Register (EAH, BANK0)                                                                                |     |

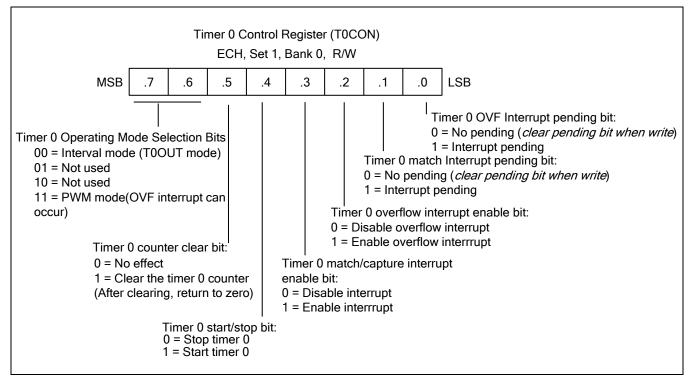

| 4.1.56 T0PS-T0 Prescaler Register (EBH, BANK0)                                                                                    |     |

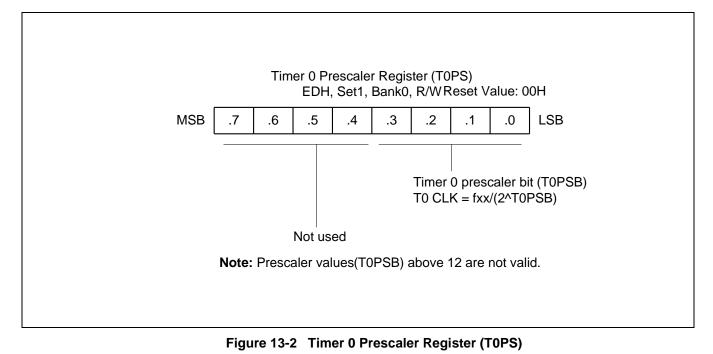

| 4.1.57 T1CON-Timer 1 Control Register (F2H, BANK0)                                                                                |     |

| 4.1.58 T1PS-T1 Prescaler Register (F3H, BANK0)                                                                                    |     |

| 4.1.59 T2CON-Timer 2 Control Register (F4H, BANK0)                                                                                |     |

| 4.1.60 T2PS-T2 Prescaler Register (F5H, BANK0)                                                                                    |     |

| 4.1.61 UART0CONH-UART 0 Control Register High Byte (00H, PAGE8)<br>4.1.62 UART0CONL-UART 0 Control Register Low Byte (01H, PAGE8) |     |

|                                                                                                                                   |     |

| 4.1.63 UART1CONH-UART 1Control Register High Byte (04H, PAGE8)<br>4.1.64 UART1CONL-UART 1 Control Register Low Byte (05H, PAGE8)  |     |

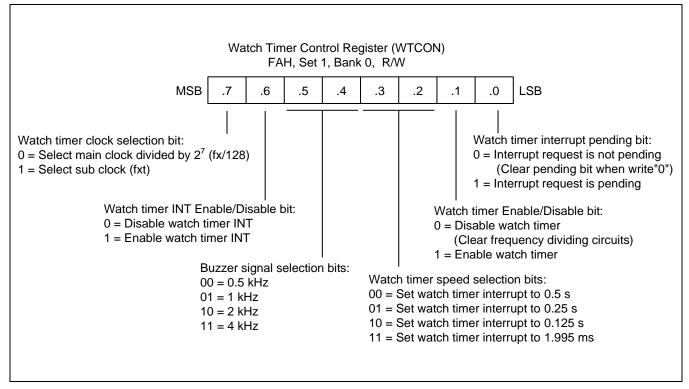

| 4.1.65 WTCON-Watch Timer Control Register (FAH, BANK0)                                                                            |     |

|                                                                                                                                   |     |

| 5 Interrupt Structure                                                                                                             |     |

| -                                                                                                                                 |     |

| 5.1 Overview                                                                                                                      |     |

| 5.1.1 Levels                                                                                                                      |     |

| 5.1.2 Vectors                                                                                                                     |     |

| 5.1.3 Sources                                                                                                                     |     |

| 5.2 Interrupt Types                                                                                                               |     |

| 5.3 S3F8S19A Interrupt Structure                                                                                                  |     |

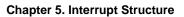

| 5.3.1 Interrupt Vector Addresses                                                                                                  |     |

| 5.3.2 Enable/Disable Interrupt Instructions (EI, DI)                                                                              |     |

| 5.4 System-Level Interrupt Control Registers                                                                                      |     |

| 5.5 Interrupt Processing Control Points                                                                                           | 5-0 |

| 5.6 Peripheral Interrupt Control Registers              |      |

|---------------------------------------------------------|------|

| 5.7 System Mode Register (SYM)                          |      |

| 5.8 Interrupt Mask Register (IMR)                       |      |

| 5.9 Interrupt Priority Register                         |      |

| 5.10 Interrupt Request Register (IRQ)                   |      |

| 5.11 Interrupt Pending Function Types                   |      |

| 5.11.1 Overview                                         |      |

| 5.11.2 Pending Bits Cleared Automatically by Hardware   |      |

| 5.11.3 Pending Bits Cleared by the Service Routine      |      |

| 5.12 Interrupt Source Polling Sequence                  |      |

| 5.12.1 Interrupt Service Routines                       |      |

| 5.12.2 Generating Interrupt Vector Addresses            |      |

| 5.12.3 Nesting of Vectored Interrupts                   |      |

| 5.12.4 Instruction Pointer                              |      |

| 5.12.5 Fast Interrupt Processing                        |      |

| 5.12.6 Procedure for Initiating Fast Interrupts         |      |

| 5.12.7 Fast Interrupt Service Routine                   |      |

| 5.12.8 Relationship to Interrupt Pending Bit Types      | 5-18 |

| 5.13 Programming Guidelines                             |      |

|                                                         |      |

| 6 Instruction Set                                       | 6-1  |

| 6.1 Overview                                            | 6-1  |

| 6.1.1 Data Types                                        |      |

| 6.1.2 Register Addressing                               |      |

| 6.1.3 Addressing Modes                                  |      |

| 6.2 Flags Register                                      |      |

| 6.3 Flag Descriptions                                   |      |

| 6.4 Instruction Set Notation                            |      |

| 6.5 Condition Codes                                     |      |

| 6.6 Instruction Descriptions                            |      |

| 6.6.1 ADC-Add with Carry                                |      |

| 6.6.2 ADD-Add with Carry<br>6.6.2 ADD-Add               |      |

|                                                         |      |

| 6.6.3 AND-Logical AND                                   |      |

| 6.6.4 BAND-Bit AND                                      |      |

| 6.6.5 BCP-Bit Compare                                   |      |

| 6.6.6 BITC-Bit Complement                               |      |

| 6.6.7 BITR-Bit Reset                                    |      |

| 6.6.8 BITS-Bit Set                                      |      |

| 6.6.9 BOR-Bit OR                                        |      |

| 6.6.10 BTJRF-Bit Test, Jump Relative on False           |      |

| 6.6.11 BTJRT-Bit Test, Jump Relative on True            |      |

| 6.6.12 BXOR-Bit XOR                                     |      |

| 6.6.13 CALL-Call Procedure                              |      |

| 6.6.14 CCF-Complement Carry Flag                        |      |

| 6.6.15 CLR-Clear                                        |      |

| 6.6.16 COM-Complement                                   |      |

| 6.6.17 CP-Compare                                       |      |

| 6.6.18 CPIJE-Compare, Increment, and Jump on Equal      |      |

| 6.6.19 CPIJNE-Compare, Increment, and Jump on Non-Equal | 6-31 |

| 6.6.20 DA-Decimal Adjust                                |      |

| 6.6.21 DA-Decimal Adjust                                |      |

| 6.6.22 DEC-Decrement                                    |      |

| 6.6.23 DECW-Decrement Word                                  | 6-35 |

|-------------------------------------------------------------|------|

| 6.6.24 DI-Disable Interrupts                                |      |

| 6.6.25 DIV-Divide (Unsigned)                                |      |

| 6.6.26 DJNZ-Decrement and Jump if Non-Zero                  |      |

| 6.6.27 El-Enable Interrupts                                 |      |

| 6.6.28 ENTER-Enter                                          |      |

| 6.6.29 EXIT-Exit                                            |      |

| 6.6.30 IDLE-Idle Operation                                  |      |

| 6.6.31 INC-Increment                                        |      |

| 6.6.32 INCW-Increment Word                                  |      |

| 6.6.33 IRET-Interrupt Return                                |      |

| 6.6.34 JP-Jump                                              |      |

| 6.6.35 JR-Jump Relative                                     |      |

| 6.6.36 LD-Load                                              |      |

| 6.6.37 LD-Load                                              |      |

| 6.6.38 LDB-Load Bit                                         |      |

| 6.6.39 LDC/LDE-Load Memory                                  |      |

| 6.6.40 LDC/LDE-Load Memory                                  |      |

| 6.6.41 LDCD/LDED-Load Memory and Decrement                  |      |

| 6.6.42 LDCI/LDEI-Load Memory and Increment                  |      |

| 6.6.43 LDCPD/LDEPD-Load Memory with Pre-Decrement           |      |

| 6.6.44 LDCPI/LDEPI-Load Memory with Pre-Increment           |      |

| 6.6.45 LDW-Load Word                                        |      |

| 6.6.46 MULT-Multiply (Unsigned)                             | 6 59 |

| 6.6.47 NEXT-Next                                            |      |

| 6.6.48 NOP-No Operation                                     |      |

| 6.6.49 OR-Logical OR                                        |      |

| 6.6.50 POP-Pop from Stack                                   |      |

| 6.6.51 POPUD-Pop User Stack (Decrementing)                  |      |

| 6.6.52 POPUI-Pop User Stack (Incrementing)                  |      |

| 6.6.53 PUSH-Push to Stack (incrementing)                    | 0-04 |

| 6.6.54 PUSHUD-Push User Stack (Decrementing)                |      |

| 6.6.55 PUSHUI-Push User Stack (Incrementing)                |      |

| 6.6.56 RCF-Reset Carry Flag                                 |      |

| 6.6.57 RET-Return                                           |      |

| 6.6.58 RL-Rotate Left                                       |      |

| 6.6.59 RLC-Rotate Left Through Carry                        | 6 74 |

| 6.6.60 RR-Rotate Right                                      |      |

| 6.6.61 RRC-Rotate Right through Carry                       |      |

| 6.6.62 SB0-Select Bank 0                                    |      |

| 6.6.63 SB1-Select Bank 1                                    |      |

|                                                             |      |

| 6.6.64 SBC-Subtract With Carry<br>6.6.65 SCF-Set Carry Flag |      |

|                                                             |      |

| 6.6.66 SRA-Shift Right Arithmetic                           |      |

| 6.6.67 SRP/SRP0/SRP1-Set Register Pointer                   |      |

| 6.6.68 STOP-Stop Operation                                  |      |

| 6.6.69 SUB-Subtract                                         |      |

| 6.6.70 SWAP-Swap Nibbles                                    | 0-02 |

| 6.6.71 TCM-Test Complement under Mask                       | 0-03 |

| 6.6.72 TM-Test under Mask                                   |      |

| 6.6.73 WFI-Wait for Interrupt                               | 0-85 |

| 6.6.74 XOR-Logical Exclusive OR                             | 6-86 |

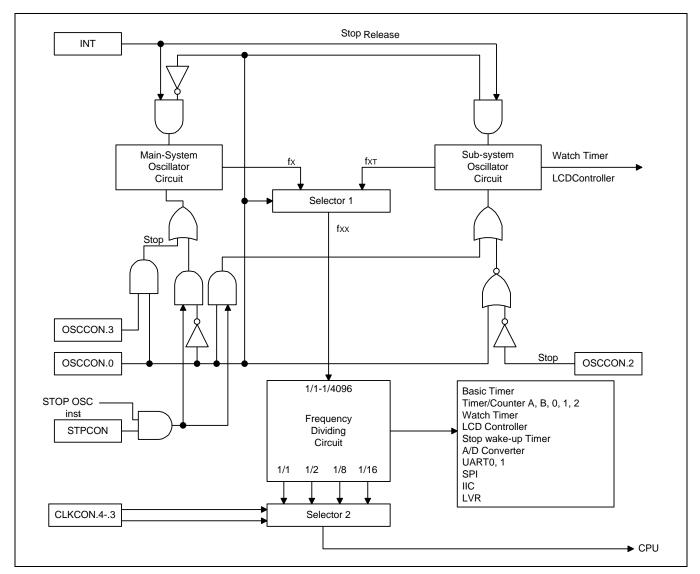

| 7 Clock Circuit                                                      | 7-1  |

|----------------------------------------------------------------------|------|

| 7.1 Overview                                                         |      |

| 7.2 System Clock Circuit                                             | 7-1  |

| 7.3 C2.Clock Status during Power-Down Modes                          |      |

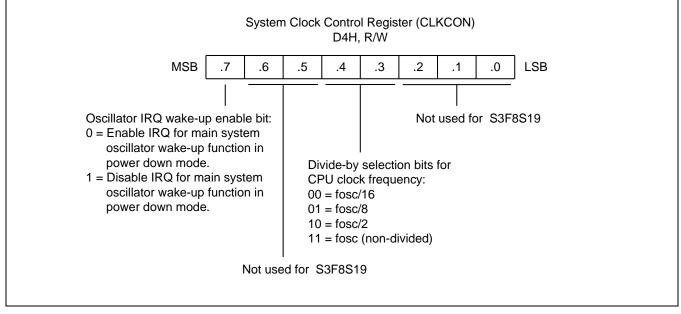

| 7.4 System Clock Control Register (CLKCON)                           |      |

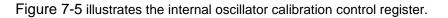

| 7.5 Internal Oscillator Calibration Control Register (OSCCALCON)     |      |

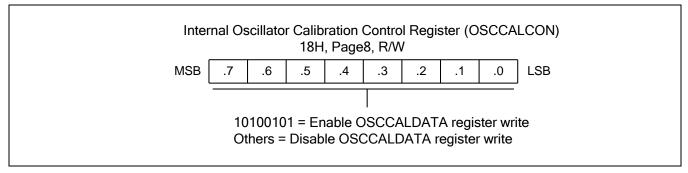

| 7.6 Internal Oscillator Calibration Data Register (OSCCALDATA)       |      |

| 7.7 Oscillator Control Register (OSCCON)                             |      |

| 7.8 Switching the CPU Clock                                          | 7-7  |

| 7.9 Ring Oscillator Control Register (ROSCCON)                       | 7-8  |

| 7.10 Stop Control Register (STPCON)                                  | 7-9  |

| 8 RESET and Power-Down                                               | 8-1  |

| 8.1 Overview                                                         |      |

| 8.1.1 MCU Initialization Sequence                                    |      |

| 8.2 Power-Down Modes                                                 |      |

| 8.2.1 Stop Mode                                                      |      |

| 8.2.2 Using RESET to Release Stop Mode                               |      |

| 8.2.3 Using an External Interrupt to Release Stop Mode               |      |

| 8.3 IDLE Mode                                                        |      |

| 8.4 Hardware Reset Values                                            |      |

| 9 Input/Output (I/O) Ports                                           | 9-1  |

| 9.1 Overview                                                         |      |

| 9.2 Port Data Registers                                              |      |

| 9.3 Port 0                                                           |      |

| 9.3.1 Port 0 Control Register (P0CONH, P0CONL)                       |      |

| 9.4 Port 1                                                           |      |

| 9.4.1 Port 1 Control Register High Byte                              |      |

| 9.4.2 Port 1 Control Register Low Byte (P1CONL)                      |      |

| 9.5 Port 2                                                           |      |

| 9.5.1 Port 2 Control Registers (P2CONH, P2CONL)                      |      |

| 9.6 Port 3                                                           |      |

| 9.6.1 Port 3 Control Register (P3CONH, P3CONL)                       |      |

| 9.6.2 Port 3 Interrupt Enable and Pending Registers (P3INT, PINTPND) |      |

| 9.6.3 Port 3 Pull-Up Resistor Enable Register (P3PUR)                |      |

| 9.6.4 Port 3 N-Channel Open-Drain Mode Register (PNE3)               |      |

| 9.7 Port 4                                                           |      |

| 9.7.1 Port 4 Control Register (P4CONH, P4CONL)                       |      |

| 9.7.2 Port 4 Pull-Up Resistor Enable Register (P4PUR)                |      |

| 9.7.3 Port 4 N-Channel Open-Drain Mode Register (PNE4)               | 9-14 |

| 10 Basic Timer                                                       |      |

| 10.1 Overview                                                        |      |

| 10.1.1 Basic Timer                                                   |      |

| 10.2 Basic Timer Control Register                                    |      |

| 10.3 Basic Timer Function Description                                |      |

| 10.3.1 Watchdog Timer Function                                       |      |

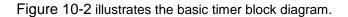

| 10.3.2 Oscillation Stabilization Interval Timer Function             | 10-3 |

| 11 8-Bit Timer A                                                     |      |

| 11.1 Overview                                                                       | 11-1 |

|-------------------------------------------------------------------------------------|------|

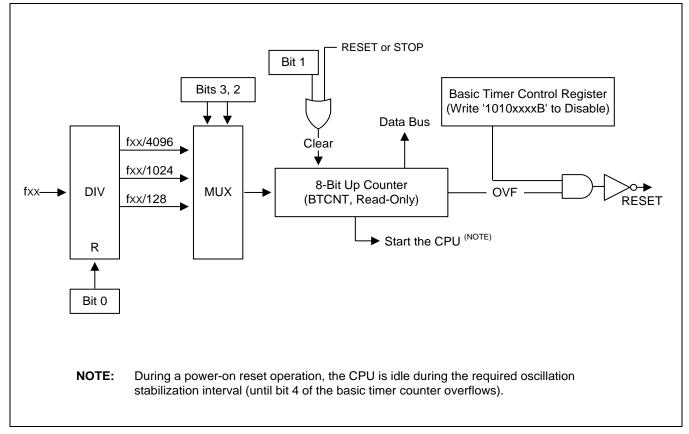

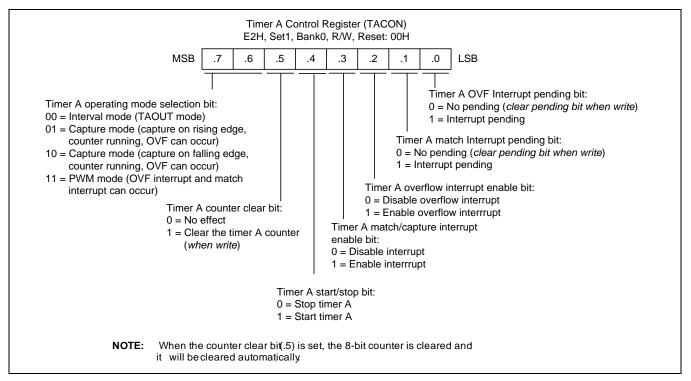

| 11.2 Timer A Control Register (TACON)                                               |      |

| 11.3 Function Description                                                           |      |

| 11.3.1 Timer A Interrupts                                                           |      |

| 11.3.2 Interval Timer Function                                                      |      |

| 11.3.3 Pulse Width Modulation Mode                                                  |      |

| 11.3.4 Capture Mode                                                                 |      |

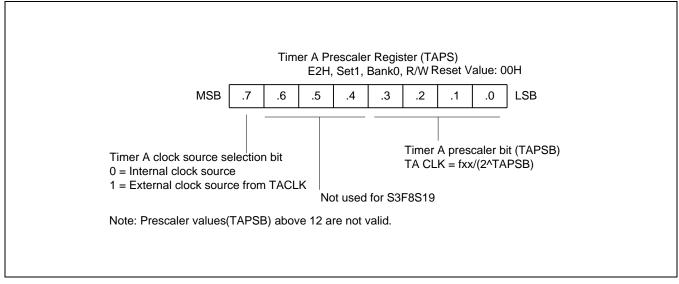

| 11.4 Block Diagram                                                                  |      |

| 12 Stop Wake-Up Timer                                                               |      |

| 12.1 Overview                                                                       | 12-1 |

| 12.1.1 Function Description                                                         |      |

| 12.1.2 Stop Wake-Up Timer Control Register                                          |      |

| 12.1.3 Stop Mode Wake Up                                                            |      |

| 13 16-Bit Timer 0/1/2/B                                                             |      |

| 13.1 Overview                                                                       | 13-1 |

| 13.2 Timer 0 Control Register                                                       |      |

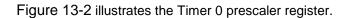

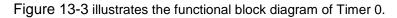

| 13.3 Block Diagram (Timer 0)                                                        |      |

| 13.4 Overview of 16-Bit Timer 1                                                     |      |

| 13.5 Timer 1 Control Register                                                       |      |

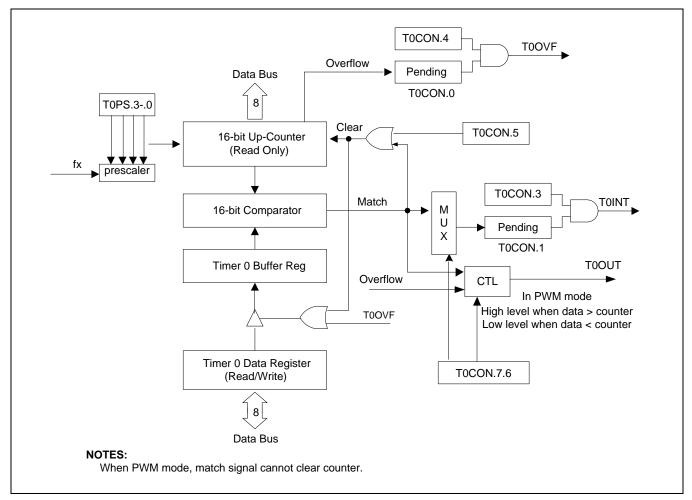

| 13.6 Timer 1 Function Description                                                   |      |

| 13.6.1 Timer 1 Interrupts (IRQ3, Vectors D8H and DAH)                               |      |

| 13.6.2 Interval Timer Mode                                                          |      |

| 13.6.3 Pulse Width Modulation Mode                                                  |      |

| 13.6.4 Capture Mode                                                                 |      |

| 13.7 Block Diagram (Timer 1)                                                        |      |

| 13.8 Overview of 16-Bit Timer 2                                                     |      |

| 13.9 Timer 2 Control Register                                                       |      |

| 13.10 Timer 2 Function Description                                                  |      |

| 13.10.1 Timer 2 Interrupts (IRQ3, Vectors DCH and DEH)                              |      |

| 13.10.2 Interval Timer Mode                                                         |      |

| 13.10.3 Pulse Width Modulation Mode                                                 |      |

| 13.10.4 Capture Mode                                                                |      |

| 13.11 Block Diagram (Timer 2)                                                       |      |

| 13.12 Overview of 16-Bit Timer B                                                    |      |

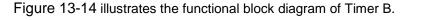

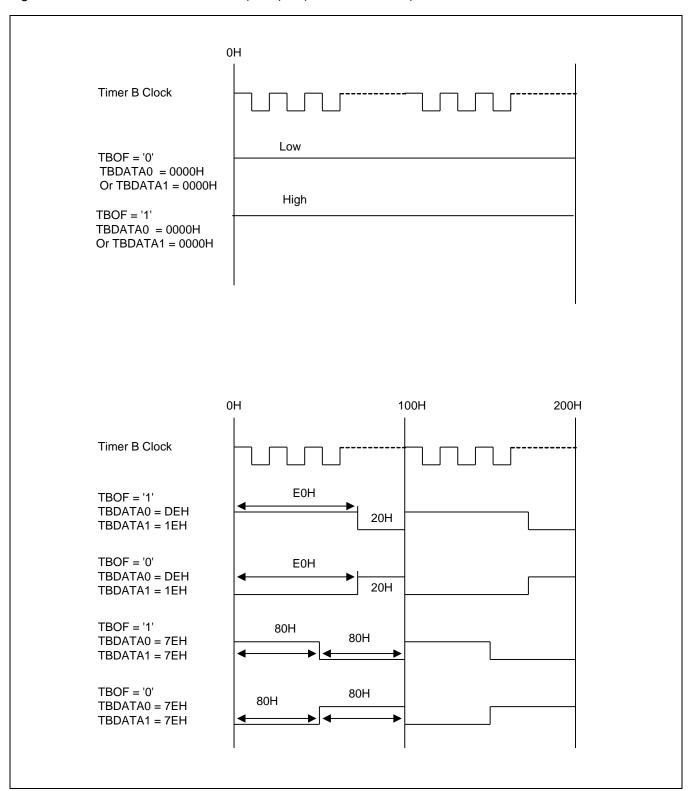

| 13.13 Block Diagram (Timer B)<br>13.13.1 Timer B Pulse Width Calculations           |      |

| 14 Watch Timer                                                                      |      |

|                                                                                     |      |

| 14.1 Overview                                                                       |      |

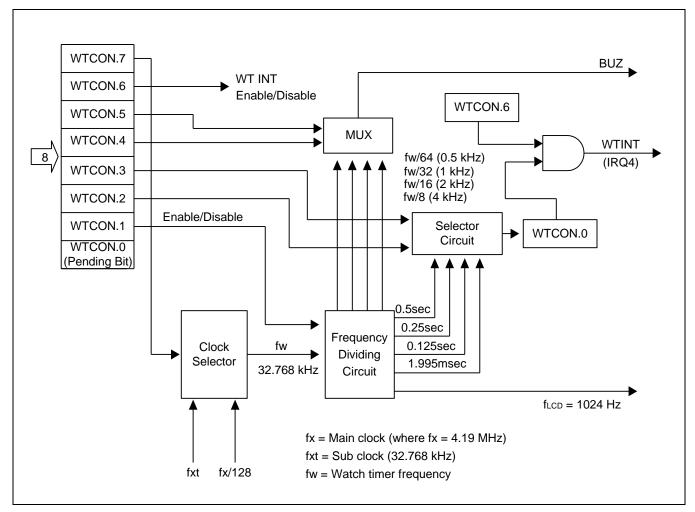

| 14.1.1 Watch Timer Control Register<br>14.1.2 Watch Timer Circuit Diagram           |      |

|                                                                                     |      |

| 15 LCD Controller/Driver                                                            |      |

| 15.1 Overview                                                                       |      |

| 15.2 LCD Circuit Diagram                                                            |      |

| 15.3 LCD RAM Address Area                                                           |      |

| 15.4 LCD Control Register (LCON)                                                    |      |

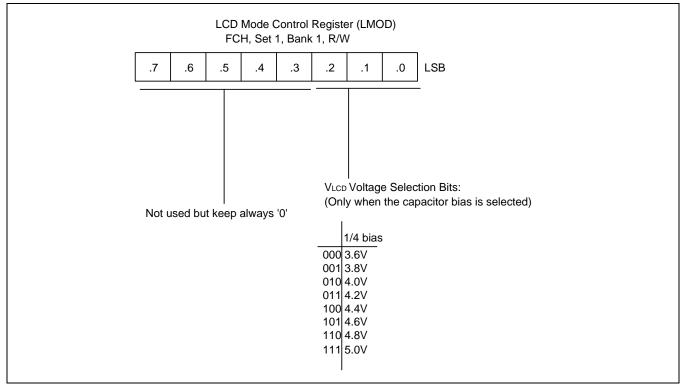

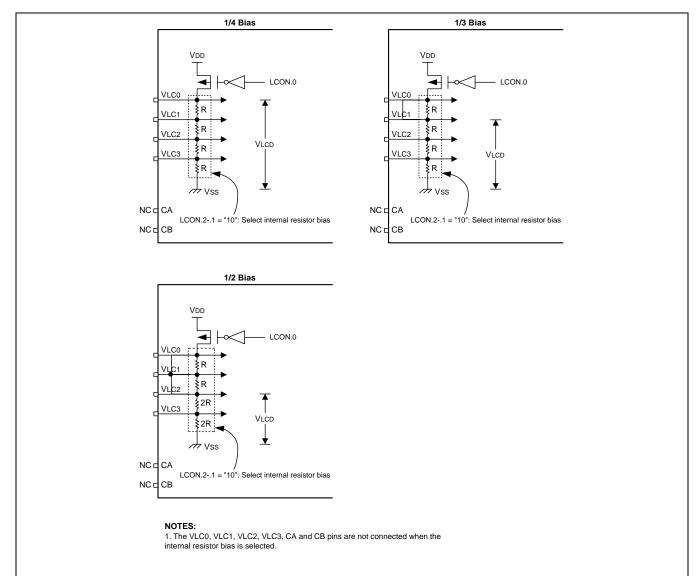

| 15.5 LCD Mode Control Register (LMOD)<br>15.6 Internal Resistor Bias Pin Connection |      |

| 10.0 III.ETTIAI INEDIDIO DIAD FIII CUTITECIIUT                                      |      |

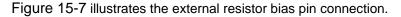

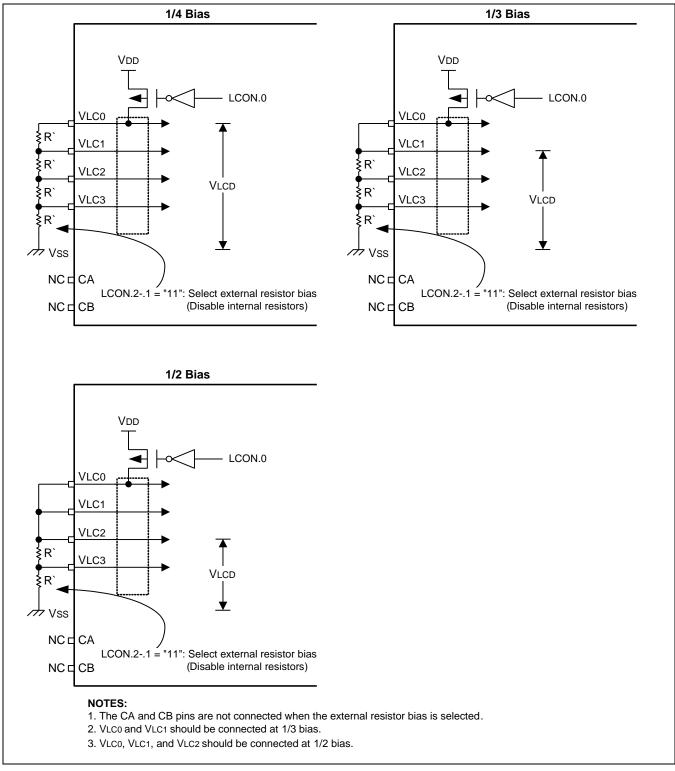

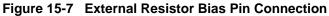

| 15.7 External Resistor Bias Pin Connection                                         |       |

|------------------------------------------------------------------------------------|-------|

| 15.8 Capacitor Bias Pin Connection                                                 | 15-10 |

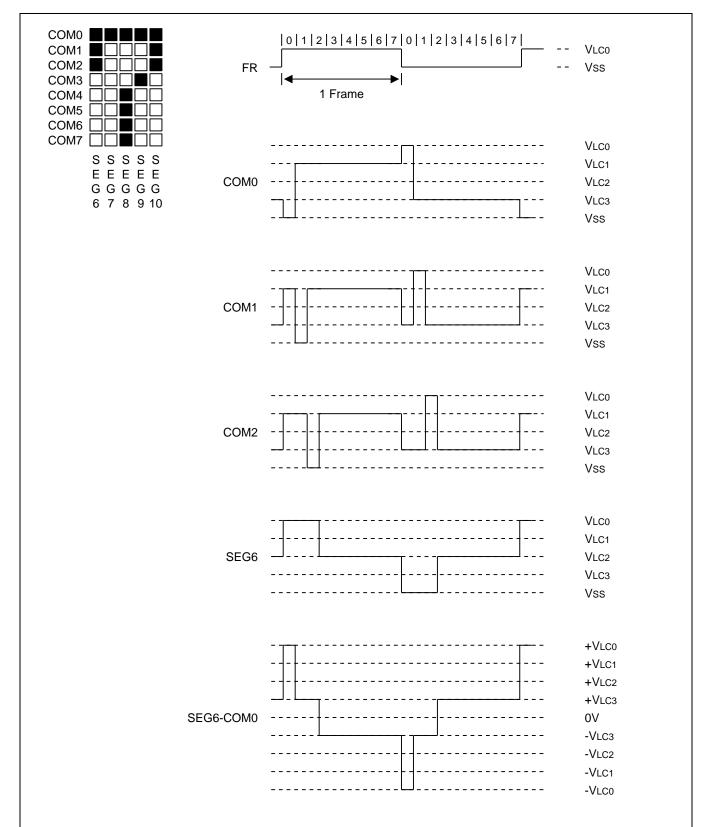

| 15.9 Common (COM) Signals                                                          |       |

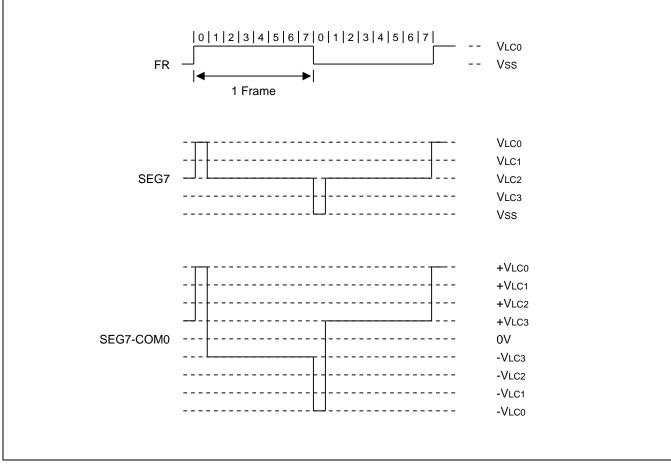

| 15.10 Segment (SEG) Signals                                                        |       |

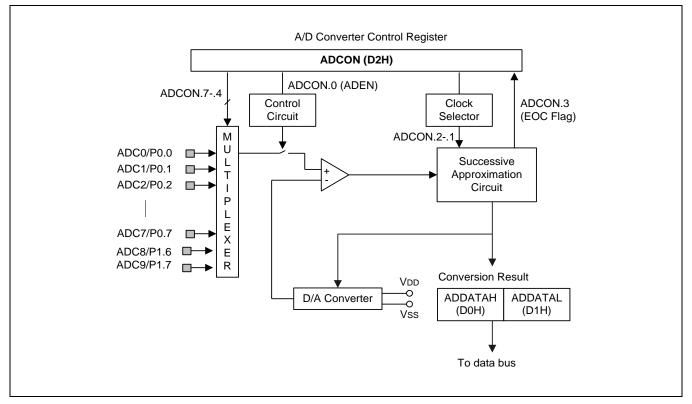

| 16 Analog/Digital Converter                                                        |       |

| 16.1 Overview                                                                      |       |

| 16.1.1 Using A/D Pins for Standard digital Input                                   |       |

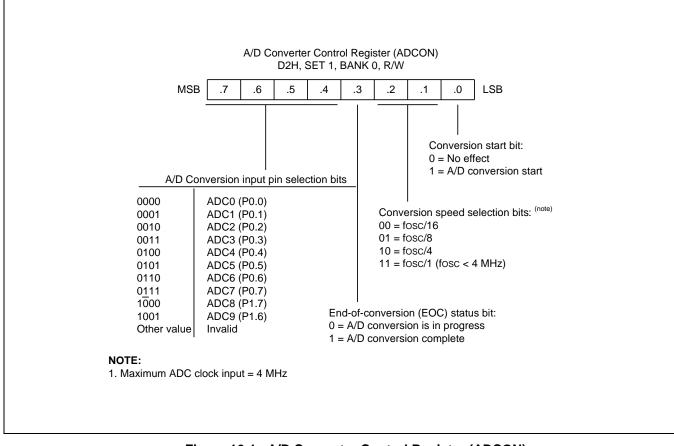

| 16.1.2 A/D Converter Control Register (ADCON)                                      |       |

| 16.1.3 Internal Reference Voltage Levels                                           |       |

| 16.1.4 Conversion timing                                                           |       |

| 16.1.5 Internal A/D Conversion Procedure                                           |       |

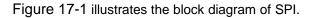

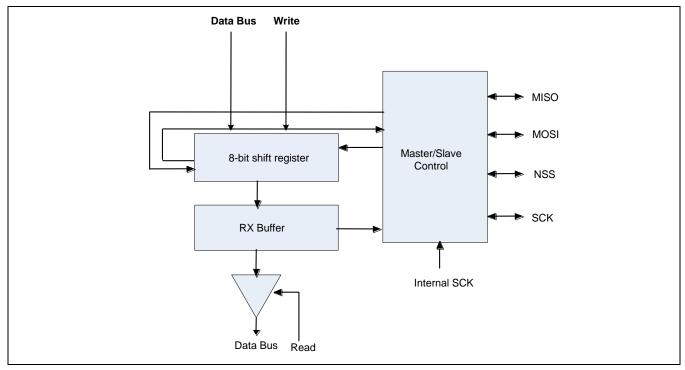

| 17 Serial Peripheral Interface                                                     |       |

| 17.1 Overview                                                                      |       |

| 17.2 Operation as an SPI Master                                                    |       |

| 17.3 Master SCK Selection                                                          |       |

| 17.4 Operation as an SPI Slave                                                     |       |

| 17.5 SPI Status and Control                                                        |       |

| 17.6 SPI Interrupt                                                                 |       |

| 17.7 SPI System Errors                                                             |       |

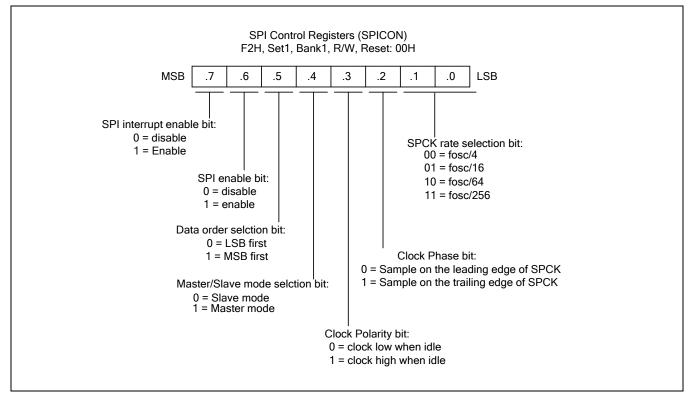

| 17.8 SPI Control Register                                                          |       |

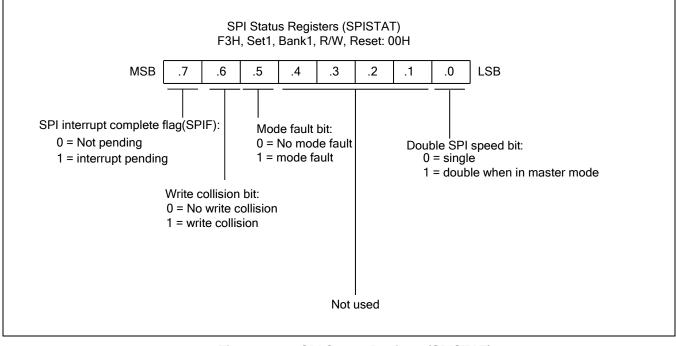

| 17.9 SPI Status Register                                                           |       |

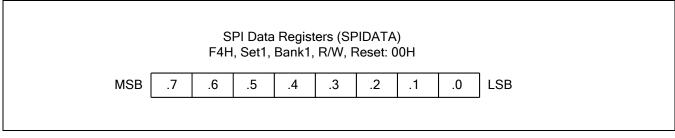

| 17.10 SPI Data Register                                                            |       |

| 18 Inter Integrated Circuit Bus Interface                                          |       |

| 18.1 Overview                                                                      |       |

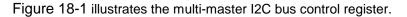

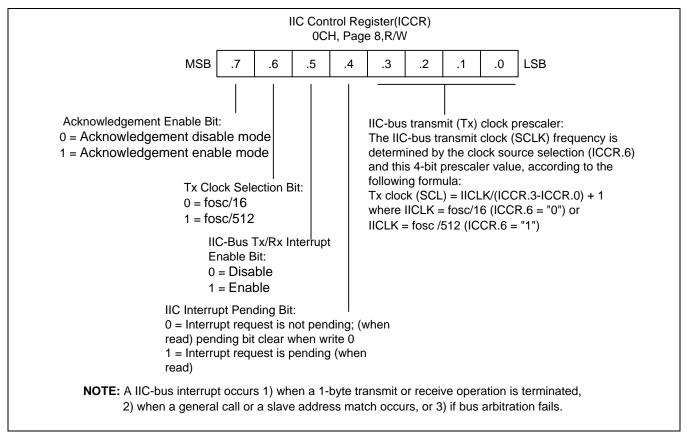

| 18.1.1 Multi-Master I2C Bus Control Register                                       |       |

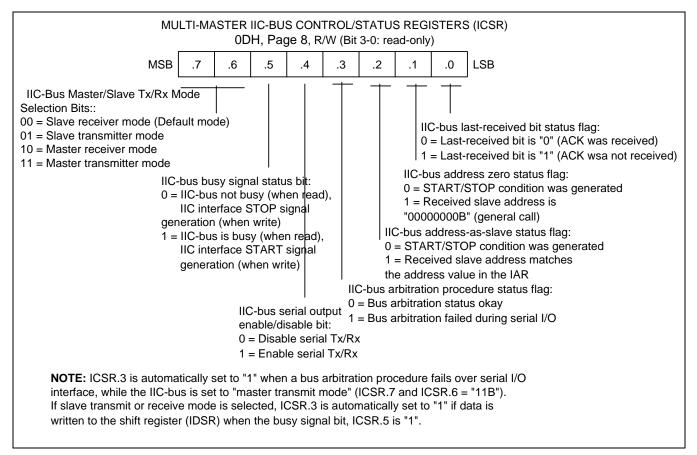

| 18.1.2 Multi-Master I2C Bus Control/Status Register                                |       |

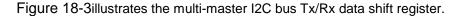

| 18.1.3 Multi-Master I2C Bus Transmit/Receive Data Shift Register                   |       |

| 18.1.4 Multi-Master I2C Bus Address Register                                       |       |

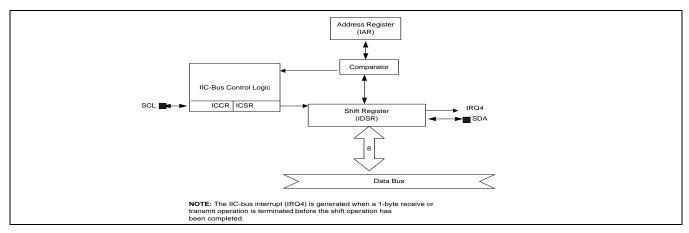

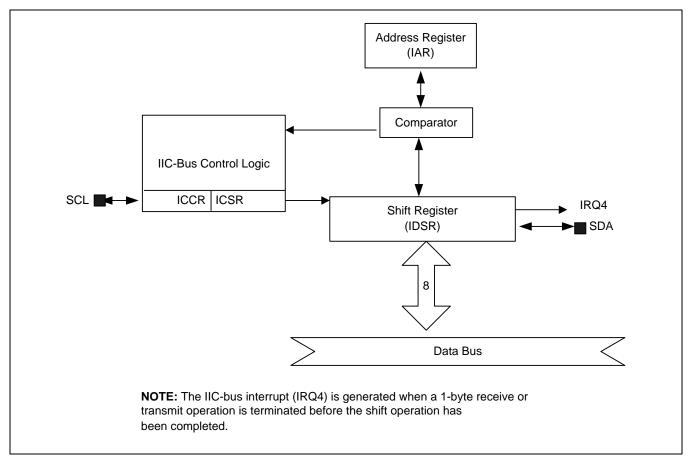

| 18.2 Block Diagram                                                                 |       |

| 18.3 The I2C Bus Interface                                                         |       |

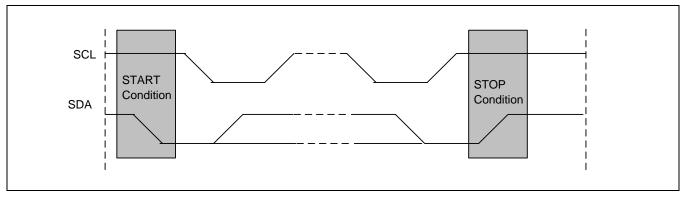

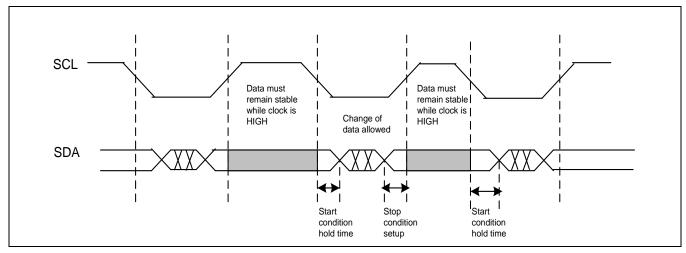

| 18.4 Start and Stop Conditions                                                     |       |

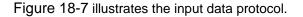

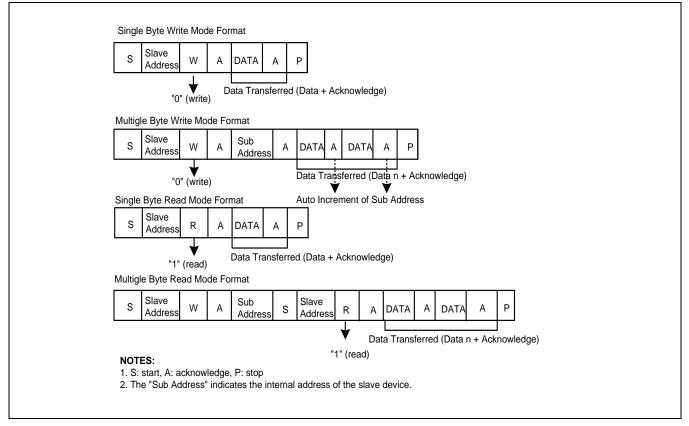

| 18.5 Data Transfer Formats                                                         |       |

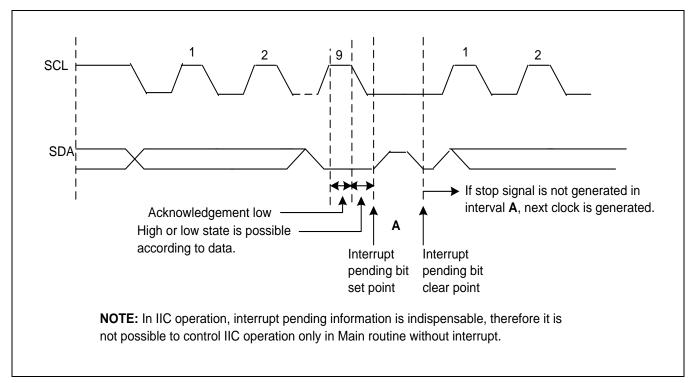

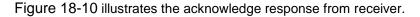

| 18.6 ACK Signal Transmission                                                       |       |

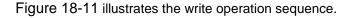

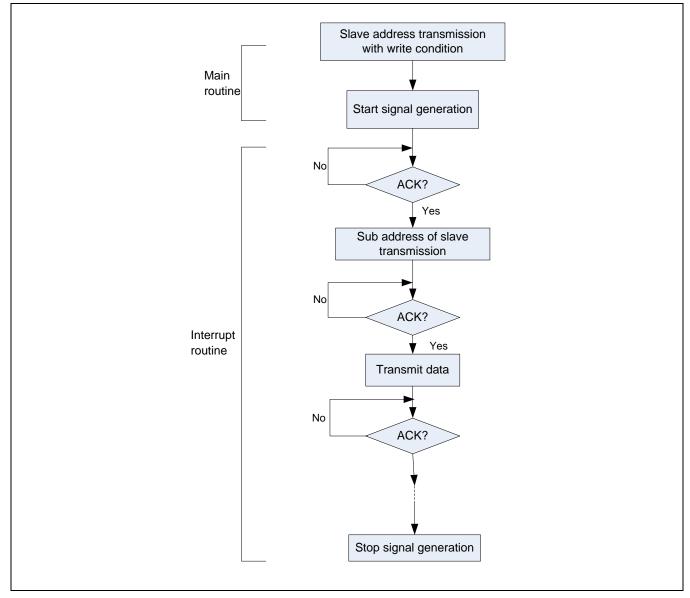

| 18.7 Read-Write Operations                                                         |       |

| 18.8 Bus Arbitration Procedures                                                    |       |

| 18.9 Abort Conditions<br>18.10 Configuring the I2C Bus                             |       |

| 19 UART 0                                                                          |       |

| 19.1 Overview                                                                      |       |

|                                                                                    |       |

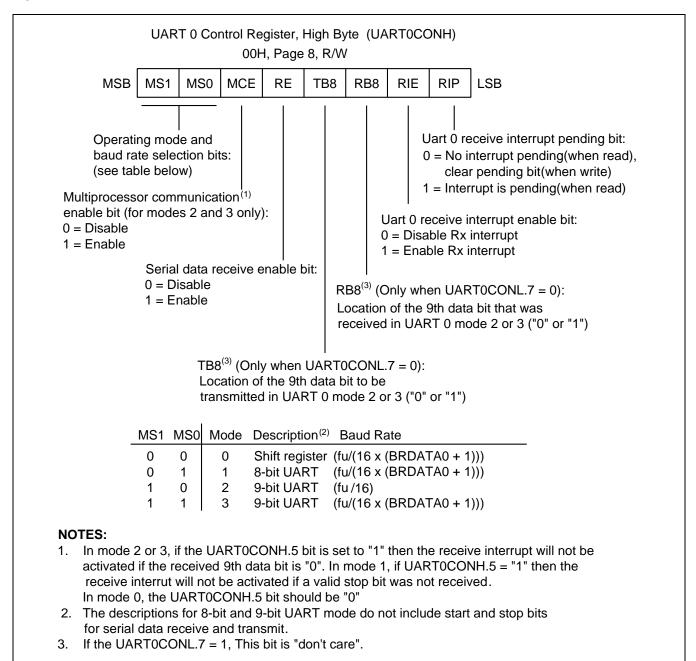

| 19.2 Programming Procedure<br>19.2.1 UART 0 High Byte Control Register (UART0CONH) |       |

| 19.2.1 UART 0 High Byte Control Register (UARTOCONH)                               |       |

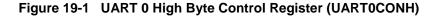

| 19.2.3 UART 0 Low Byte Control Register                                            |       |

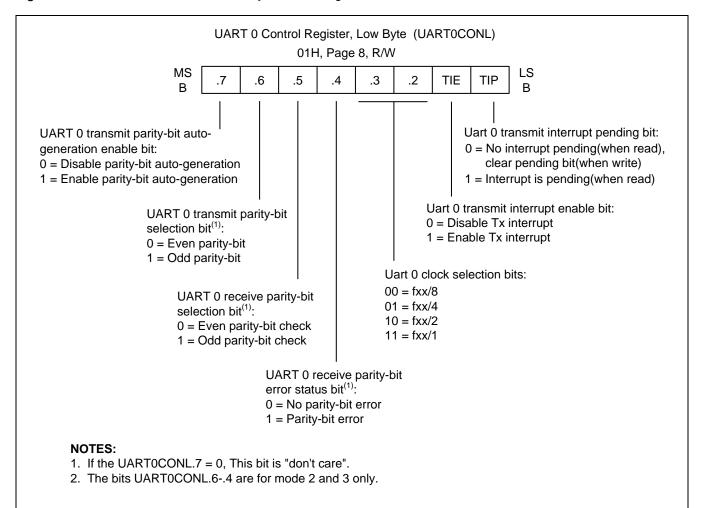

| 19.2.4 UART 0 Data Register                                                        |       |

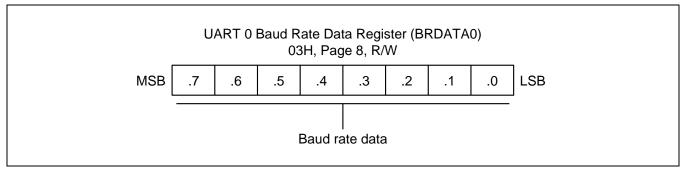

| 19.2.5 UART 0 Baud Rate Data Register                                              |       |

| 19.3 Baud Rate Calculations                                                        |       |

| 19.3.1 Mode 0 Baud Rate Calculation                                                |       |

| 19.3.2 Mode 2 Baud Rate Calculation                         |               |

|-------------------------------------------------------------|---------------|

| 19.3.3 Mode 1 and 3 Baud Rate Calculation                   |               |

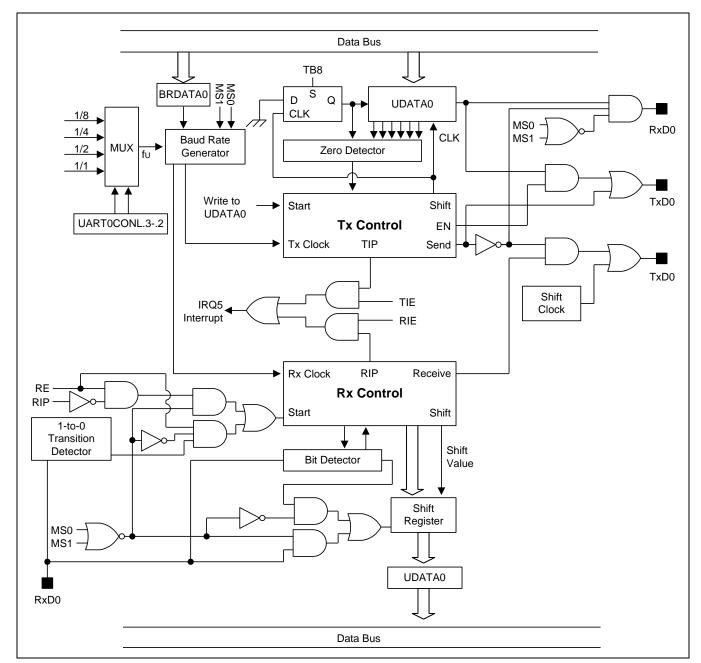

| 19.4 Block Diagram                                          |               |

| 19.5 UART 0 Mode 0 Function Description                     |               |

| 19.5.1 Mode 0 Transmit Procedure                            |               |

| 19.5.2 Mode 0 Receive Procedure                             |               |

| 19.6 Serial Port Mode 1 Function Description                |               |

| 19.6.1 Mode 1 Transmit Procedure                            |               |

| 19.6.2 Mode 1 Receive Procedure                             |               |

| 19.7 Serial Port Mode 2 Function Description                |               |

| 19.7.1 Mode 2 Transmit Procedure                            |               |

| 19.7.2 Mode 2 Receive Procedure                             |               |

| 19.8 Serial Port Mode 3 Function Description                |               |

| 19.8.1 Mode 3 Transmit Procedure                            |               |

| 19.8.2 Mode 3 Receive Procedure                             |               |

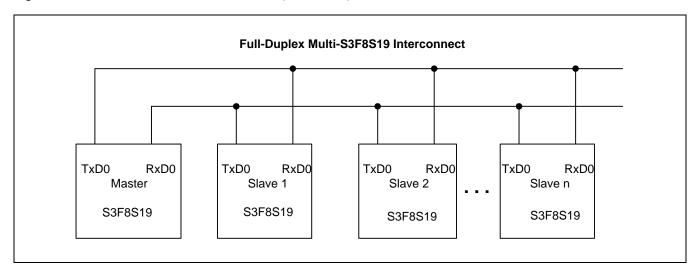

| 19.9 Serial Communication for Multiprocessor Configurations |               |

| 19.9.1 Sample Protocol for Master/Slave Interaction         |               |

| 19.9.2 Setup Procedure for Multiprocessor Communications    |               |

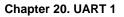

| 20 UART 1                                                   |               |

| 20.1 Overview                                               | 20-1          |

| 20.2 Programming Procedure                                  |               |

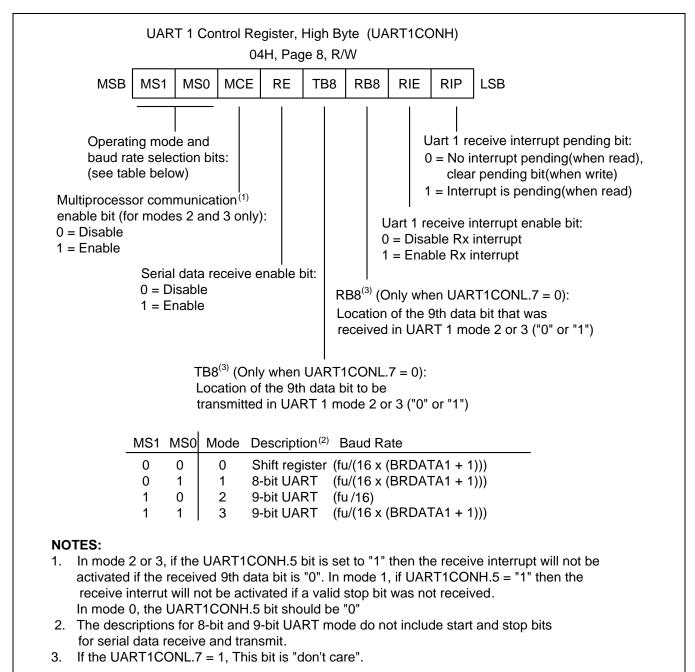

| 20.2.1 UART 1 High Byte Control Register (UART1CONH)        | 20-2          |

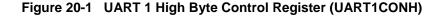

| 20.2.2 UART 1 Low Byte Control Register                     |               |

| 20.2.3 UART 1 Interrupt Pending bits                        |               |

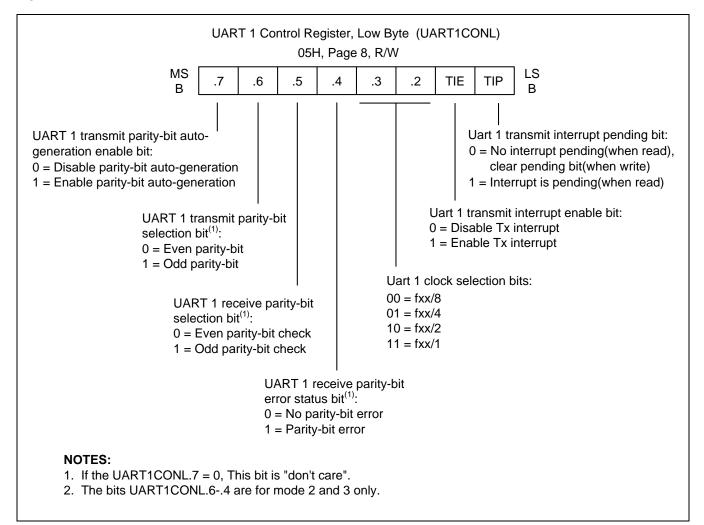

| 20.2.4 UART 1 Data Register                                 |               |

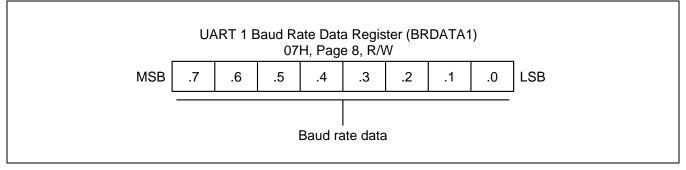

| 20.2.5 UART 1 Baud Rate Data Register                       |               |

| 20.3 Baud Rate Calculations                                 |               |

| 20.3.1 Mode 0 Baud Rate Calculation                         |               |

| 20.3.2 Mode 2 Baud Rate Calculation                         |               |

| 20.3.3 Modes 1 and 3 Baud Rate Calculation                  |               |

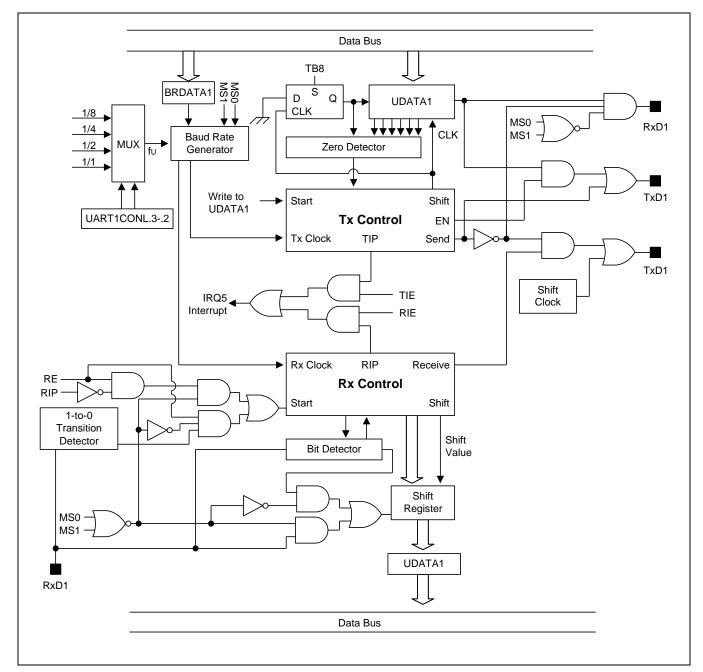

| 20.4 Block Diagram                                          |               |

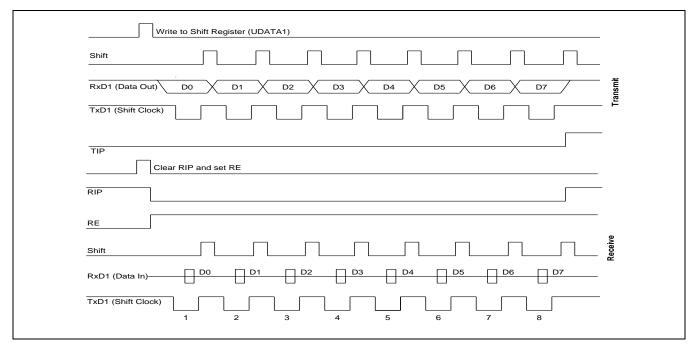

| 20.5 UART 1 Mode 0 Function Description                     |               |

| 20.5.1 Mode 0 Transmit Procedure                            |               |

| 20.5.2 Mode 0 Receive Procedure                             |               |

| 20.6 Serial Port Mode 1 Function Description                | 20-0<br>20-10 |

| 20.6.1 Mode 1 Transmit Procedure                            |               |

| 20.6.2 Mode 1 Receive Procedure                             |               |

| 20.7 Serial Port Mode 2 Function Description                |               |

| 20.7.1 Mode 2 Transmit Procedure                            |               |

| 20.7.2 Mode 2 Receive Procedure                             |               |

| 20.8 Serial Port Mode 3 Function Description                |               |

| 20.8.1 Mode 3 Transmit Procedure                            |               |

| 20.8.2 Mode 3 Receive Procedure                             |               |

| 20.9 Serial Communication for Multiprocessor Configurations |               |

| 20.9 Serial Communication for Multiprocessor Computations   |               |

| 20.9.1 Sample Protocol for Master/Slave Interaction         |               |

| 21 Embedded Flash Memory Interface                          |               |

| -                                                           |               |

| 21.1 Overview                                               |               |

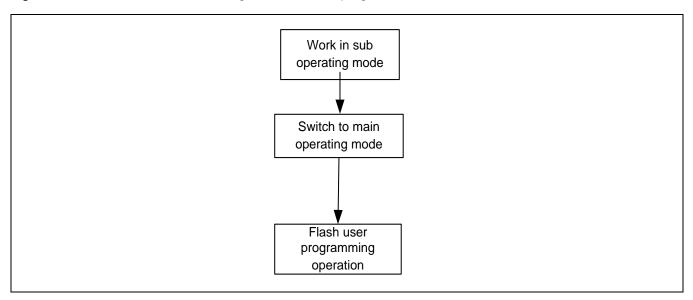

| 21.2 User Program Mode                                      |               |

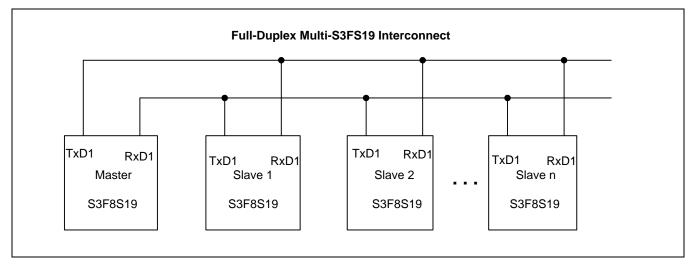

| 21.2.1 Flash Memory Control Register                 | 21-3 |

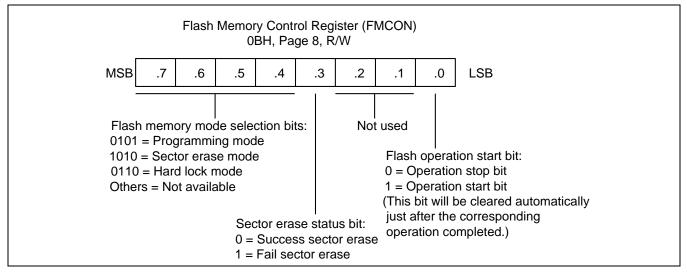

|------------------------------------------------------|------|

| 21.2.2 Flash Memory User Programming Enable Register |      |

| 21.2.3 Flash Memory Sector Address Registers         |      |

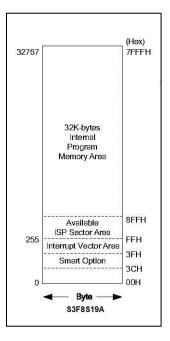

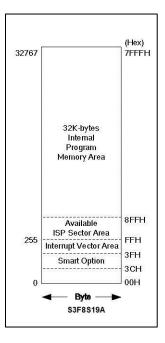

| 21.3 ISP (On-Board Programming) Sector               |      |

| 21.4 ISP Reset Vector and ISP Sector Size            |      |

| 21.5 Sector Erase                                    |      |

| 21.6 Programming                                     |      |

| 21.7 Reading                                         |      |

| 21.8 Hard Lock Protection                            |      |

| 22 Low Voltage Detect/Low Voltage Reset              |      |

| 22.1 Low Voltage Reset                               |      |

| 22.2 Low Voltage Detect                              |      |

| 23 Electrical Data                                   |      |

| 23.1 Overview                                        | 23-1 |

| 23.2 Absolute Maximum Ratings                        |      |

| 23.3 DC Electrical Characteristics                   |      |

| 23.4 AC Electrical Characteristics                   |      |

| 23.5 Oscillator Characteristics                      |      |

| 23.6 AEC Qualification                               |      |

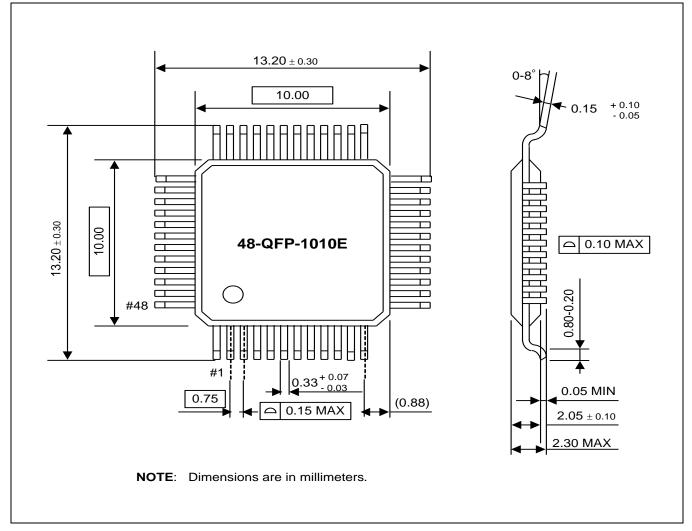

| 24 Mechanical Data                                   |      |

| 24.1 Overview                                        |      |

| 25 S3F8S19A Flash MCU                                |      |

| 25.1 Overview                                        |      |

| 25.2 Pin Assignments                                 |      |

| 25.3 On Board Writing                                |      |

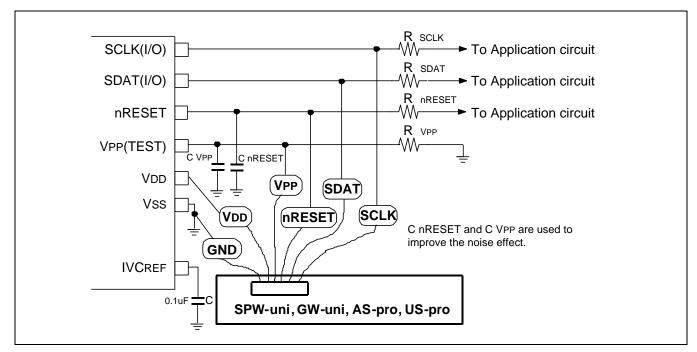

| 25.3.1 Circuit Design Guide                          |      |

| 25.3.2 Reference Table for Connection                |      |

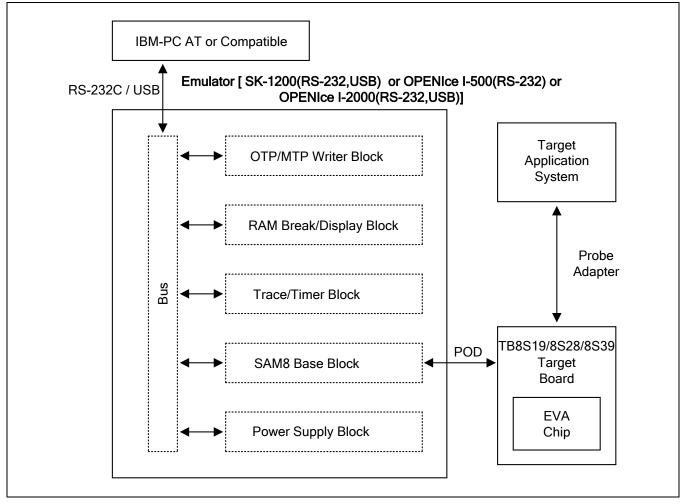

| 26 Development Tools                                 |      |

| 26.1 Overview                                        |      |

| 26.1.1 Target Boards                                 |      |

| 26.1.2 Programming Socket Adapter                    |      |

| 26.2 Third Parties for Development Tools             |      |

| 26.2.1 In-Circuit Emulators                          |      |

| 26.2.2 OTP/MTP Programmer                            |      |

Page

Number

# **List of Figures**

Title

## Figure Number

| Figure 1-1  | S3F8S19A Block Diagram                                          |     |

|-------------|-----------------------------------------------------------------|-----|

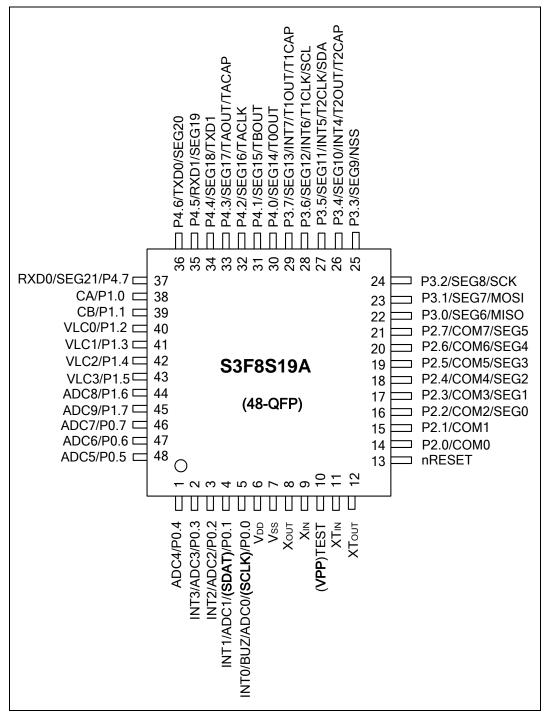

| Figure 1-2  | S3F8S19A Pin Assignments (48-QFP)                               | 1-7 |

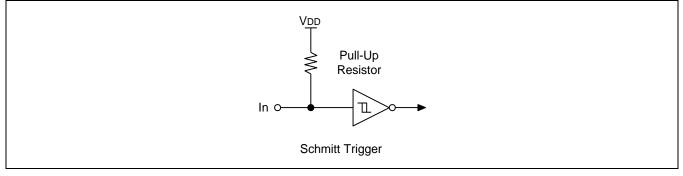

| Figure 1-3  | Pin Circuit Type A                                              |     |

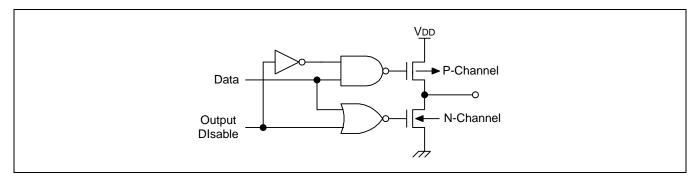

| Figure 1-4  | Pin Circuit Type B                                              |     |

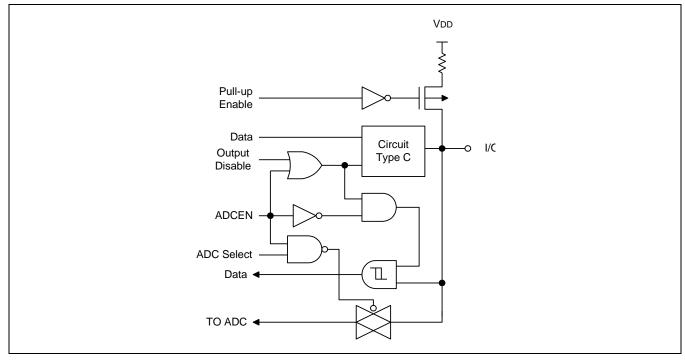

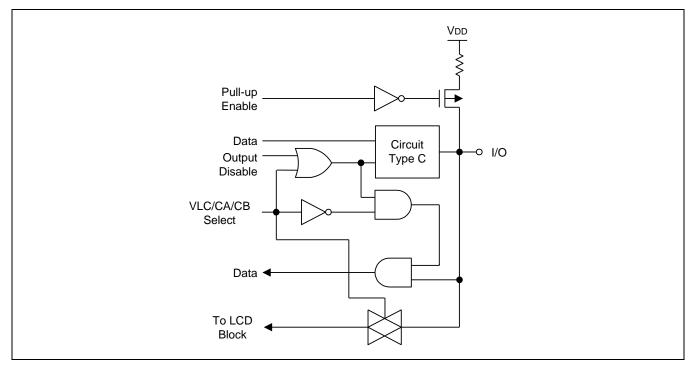

| Figure 1-5  | Pin Circuit Type C                                              |     |

| Figure 1-6  | Pin Circuit Type F-16 (P0)                                      |     |

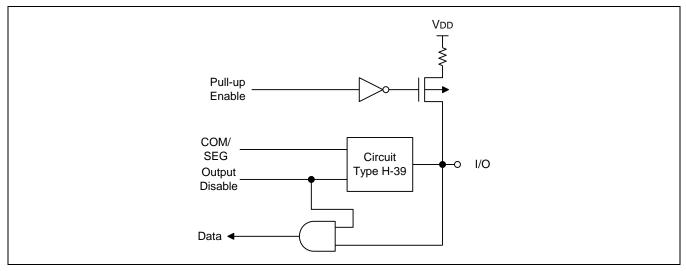

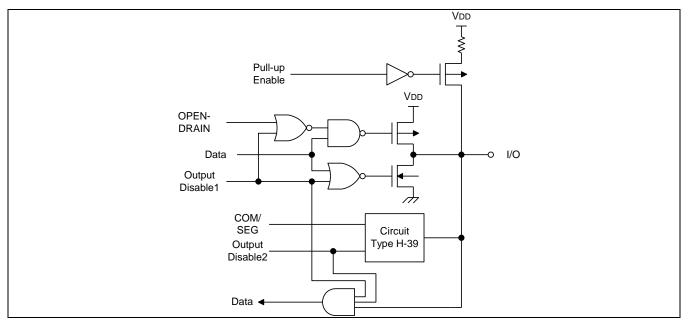

| Figure 1-7  | Pin Circuit Type H-39                                           |     |

| Figure 1-8  | Pin Circuit Type H-44 (P2)                                      |     |

| Figure 1-9  | Pin Circuit Type F-17(P1)                                       |     |

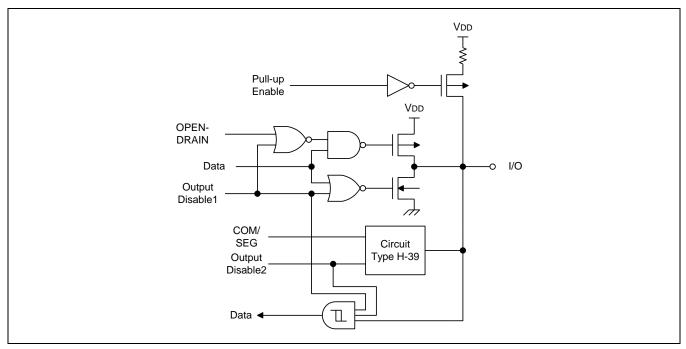

| Figure 1-10 |                                                                 |     |

| Figure 1-11 |                                                                 |     |

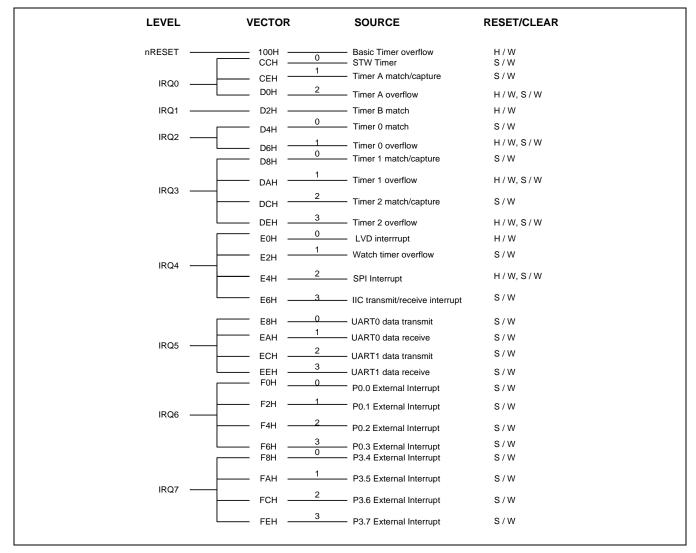

| Figure 2-1  | Program Memory Address Space                                    |     |

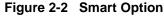

| Figure 2-2  | Smart Option                                                    |     |

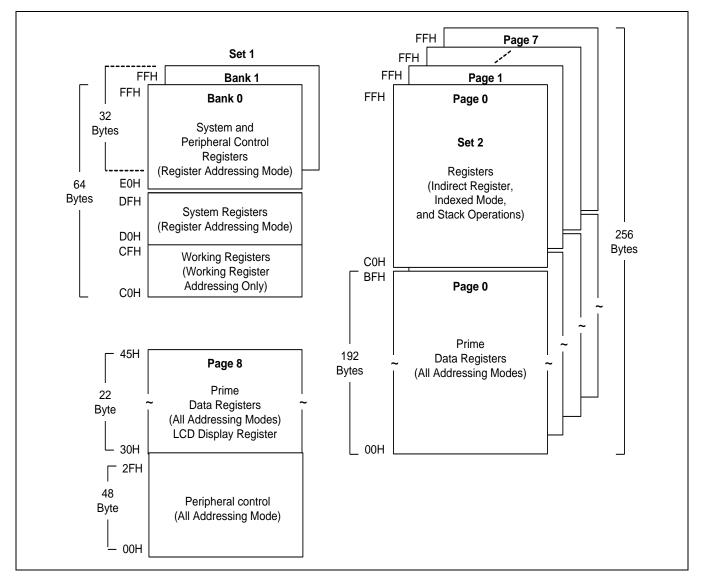

| Figure 2-3  | Internal Register File Organization (S3F8S19A)                  |     |

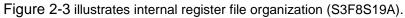

| Figure 2-4  | Register PP                                                     |     |

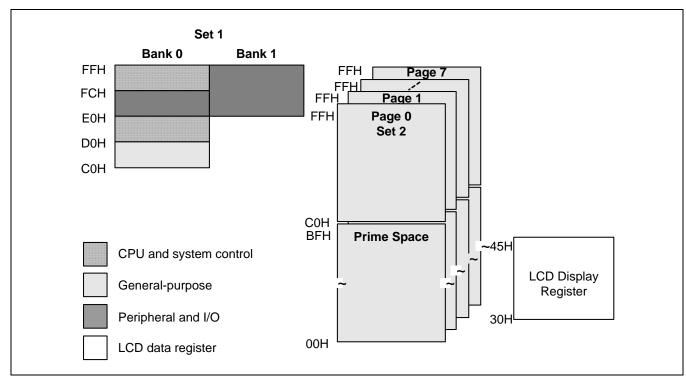

| Figure 2-5  | Set 1, Set 2, Prime Area Register Map and LCD Data Register Map |     |

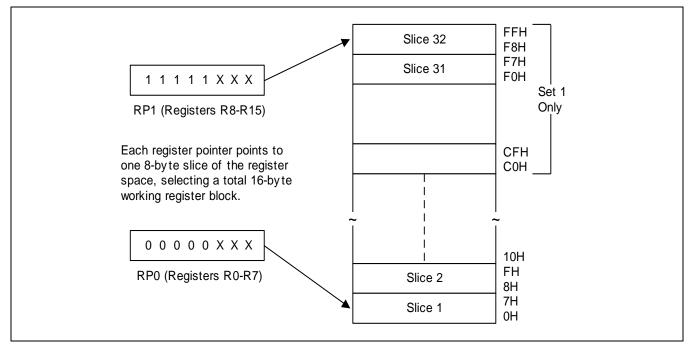

| Figure 2-6  | 8 Byte Working Register Areas (Slices)                          |     |

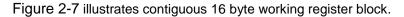

| Figure 2-7  | Contiguous 16-Byte Working Register Block                       |     |

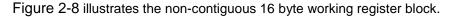

| Figure 2-8  | Non-Contiguous 16-Byte Working Register Block                   |     |

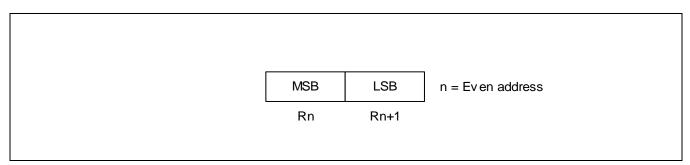

| Figure 2-9  | 16-Bit Register Pair                                            |     |

| Figure 2-10 |                                                                 |     |

| Figure 2-11 | 0 0                                                             |     |

| Figure 2-12 |                                                                 |     |

| Figure 2-13 |                                                                 |     |

| Figure 2-14 |                                                                 |     |

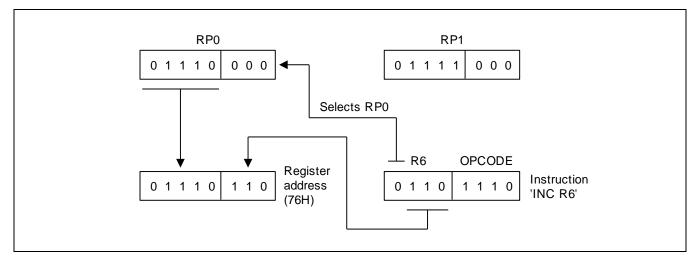

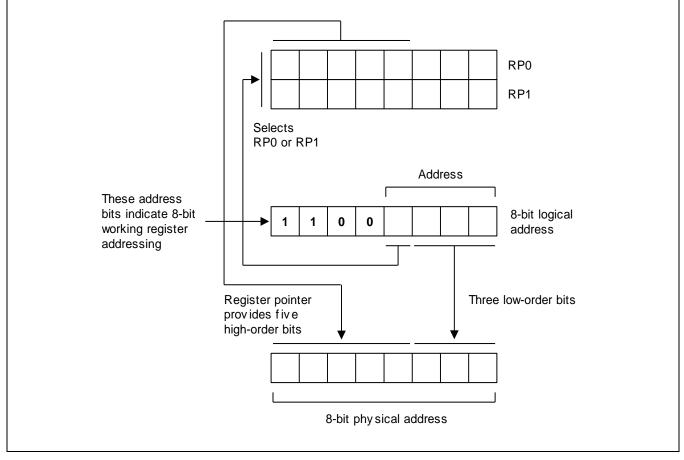

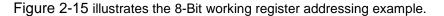

| Figure 2-15 |                                                                 |     |

| Figure 2-16 | •                                                               |     |

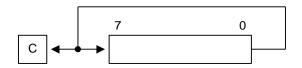

| Figure 3-1  | Register Addressing                                             |     |

| Figure 3-2  | Working Register Addressing                                     |     |

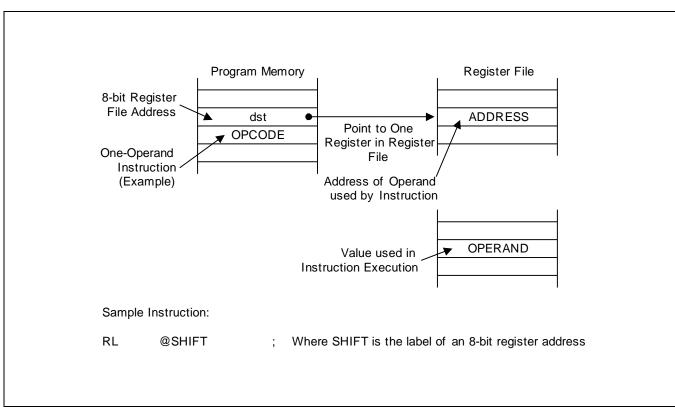

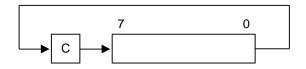

| Figure 3-3  | Indirect Register Addressing to Register File                   |     |

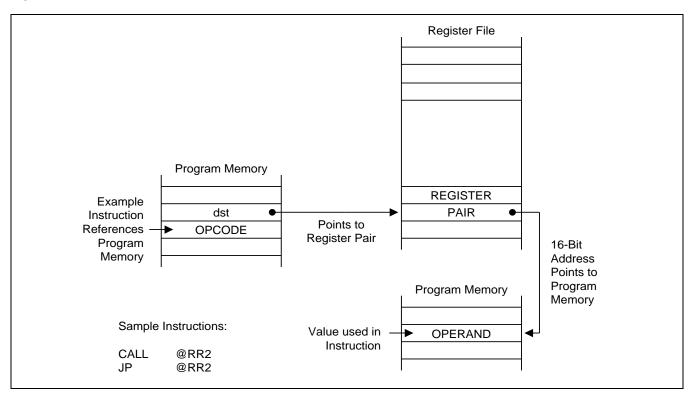

| Figure 3-4  | Indirect Register Addressing to Program Memory                  |     |

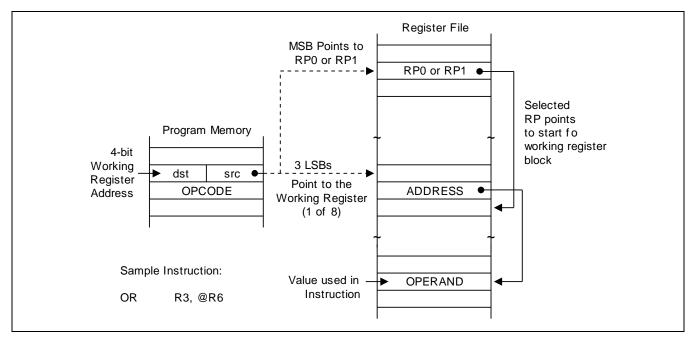

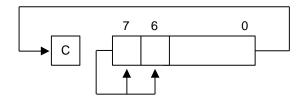

| Figure 3-5  | Indirect Working Register Addressing to Register File           |     |

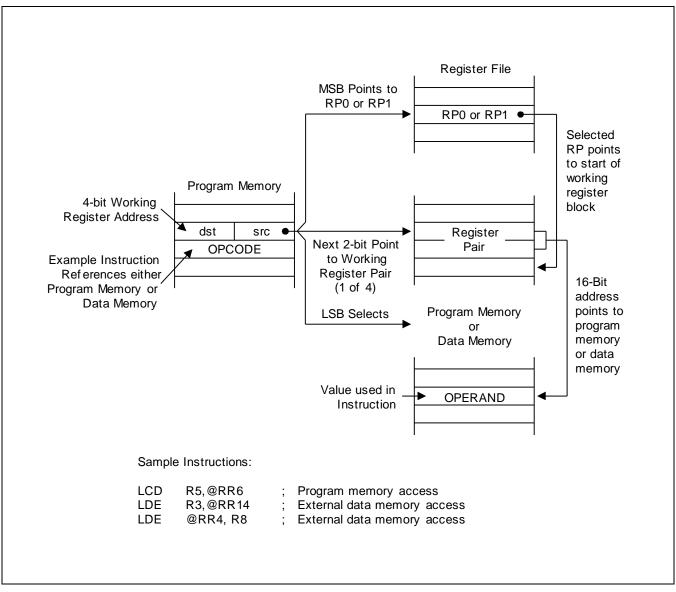

| Figure 3-6  | Indirect Working Register Addressing to Program or Data Memory  |     |

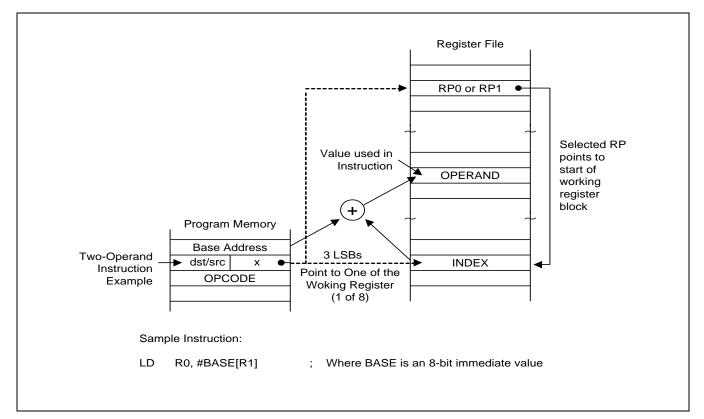

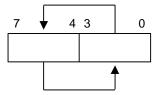

| Figure 3-7  | Indexed Addressing to Register File                             |     |

| Figure 3-8  | Indexed Addressing to Program or Data Memory with Short Offset  |     |

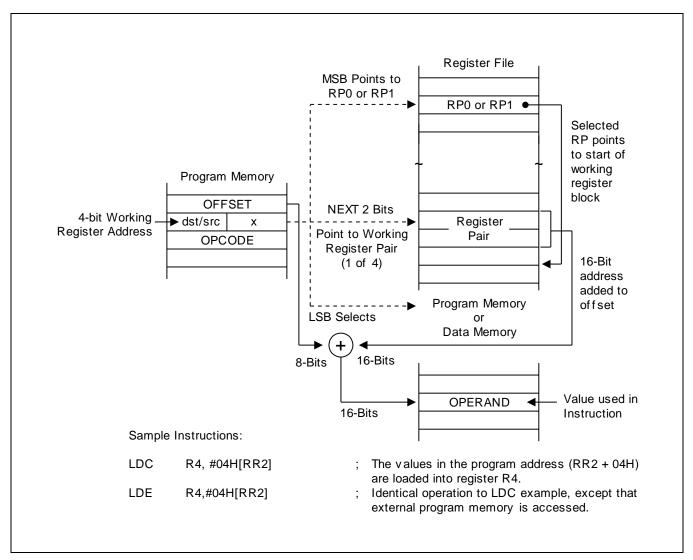

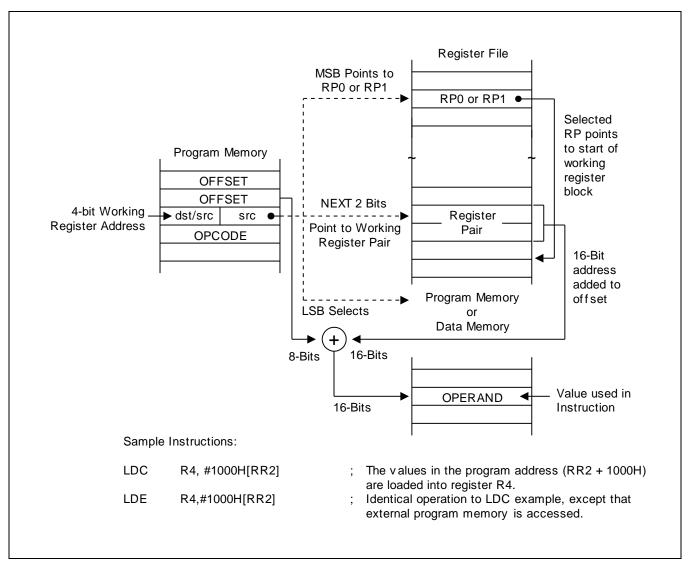

| Figure 3-9  | Indexed Addressing to Program or Data Memory                    |     |

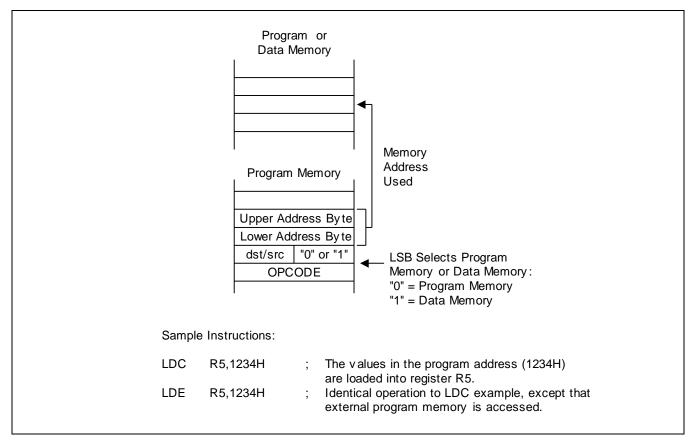

| Figure 3-10 |                                                                 |     |

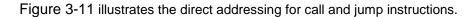

| Figure 3-11 |                                                                 |     |

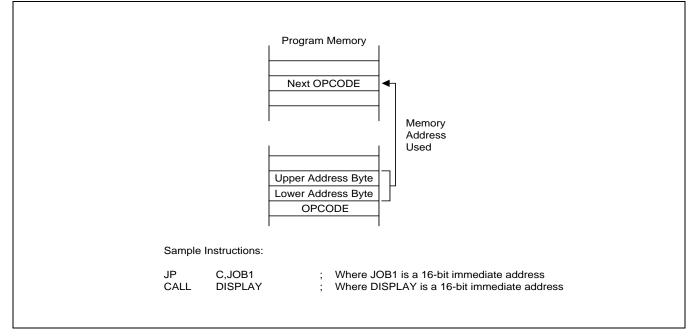

| Figure 3-12 | •                                                               |     |

| Figure 3-13 |                                                                 |     |

| Figure 3-14 | <b>U</b>                                                        |     |

| Figure 4-1  | Register Description Format                                     |     |

| Figure 5-1                 | S3C8/S3F8 Series Interrupt Types                                | 5-2  |

|----------------------------|-----------------------------------------------------------------|------|

| •                          | S3F8S19A Interrupt Structure                                    |      |

| •                          | ROM Vector Address Area                                         |      |

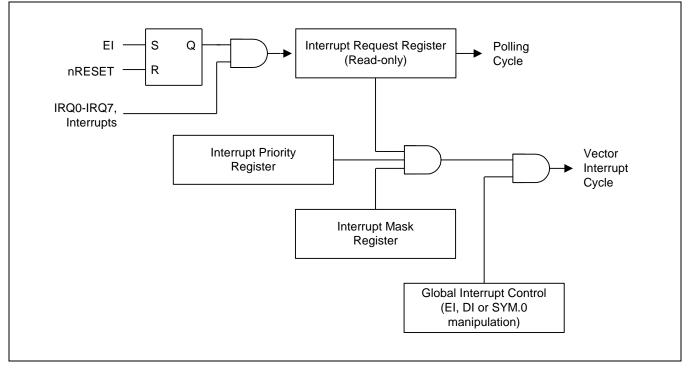

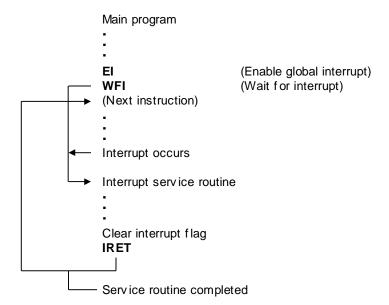

|                            | Interrupt Function Diagram                                      |      |

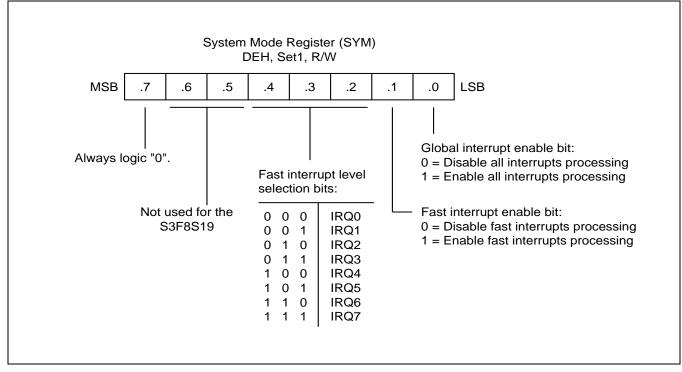

|                            | System Mode Register (SYM)                                      |      |

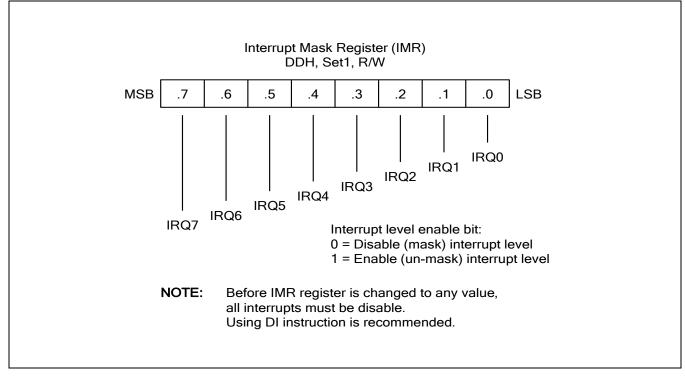

| Figure 5-6                 | Interrupt Mask Register (IMR)                                   |      |

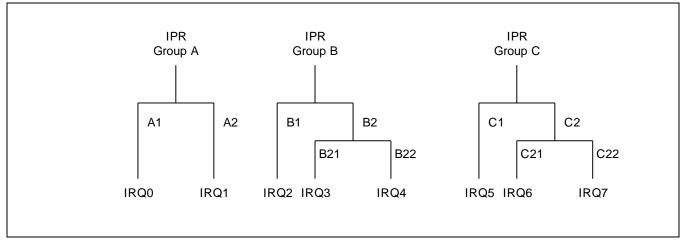

| Figure 5-7                 | Interrupt Request Priority Groups                               |      |

| Figure 5-8                 | Interrupt Priority Register (IPR)                               |      |

| Figure 5-9                 | Interrupt Request Register (IRQ)                                |      |

| Figure 6-1                 | System Flags Register (FLAGS)                                   |      |

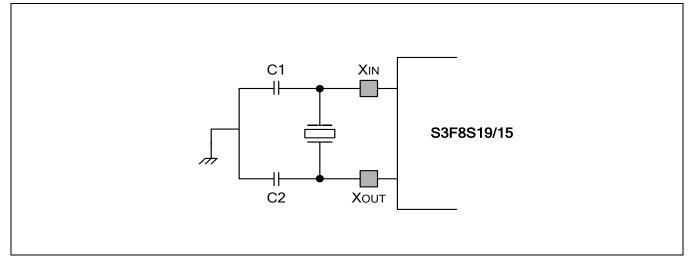

| Figure 7-1                 | Main Oscillator Circuit (RC Oscillator with Internal Capacitor) |      |

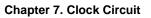

| Figure 7-2                 | Main Oscillator Circuit (Crystal/Ceramic Oscillator)            |      |

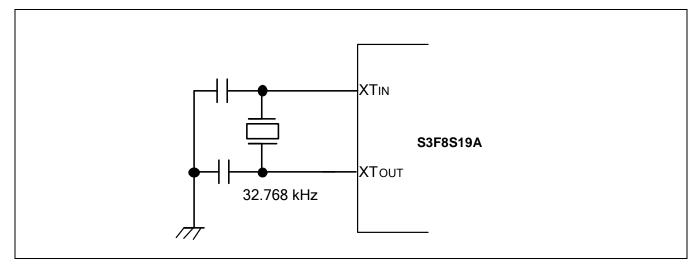

|                            | Sub-System Oscillator Circuit (Crystal Oscillator)              |      |

|                            | System Clock Control Register (CLKCON)                          |      |

|                            | Internal Oscillator Calibration Control Register (OSCCALCON)    |      |

|                            |                                                                 |      |

|                            | Internal Oscillator Calibration Data Register (OSCCALDATA)      |      |

|                            | Oscillator Control Register (OSCCON)                            |      |

| •                          | Ring Oscillator Control Register (ROSCCON)                      |      |

| <b>U</b>                   | STOP Control Register (STPCON)                                  |      |

|                            | System Clock Circuit Diagram                                    |      |

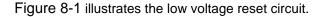

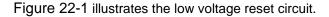

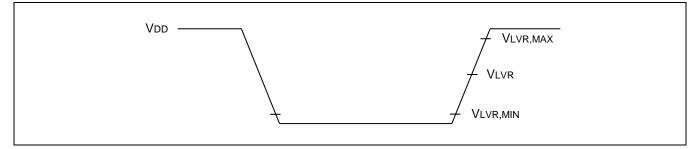

| 0                          | Low Voltage Reset Circuit                                       |      |

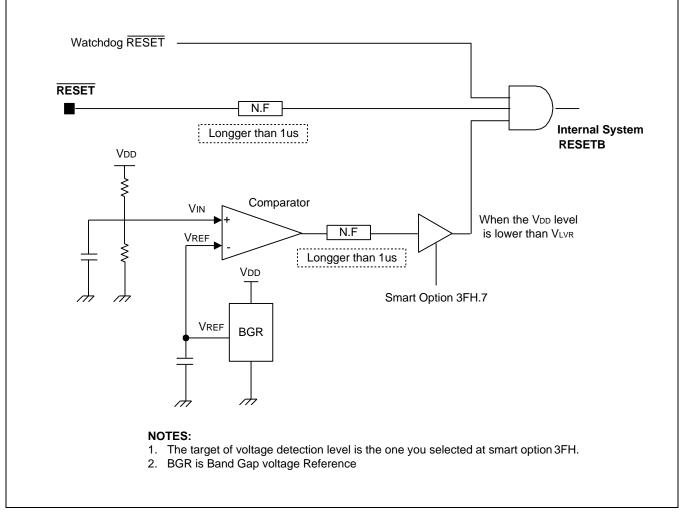

| Figure 8-2                 | Reset Block Diagram                                             | 8-3  |

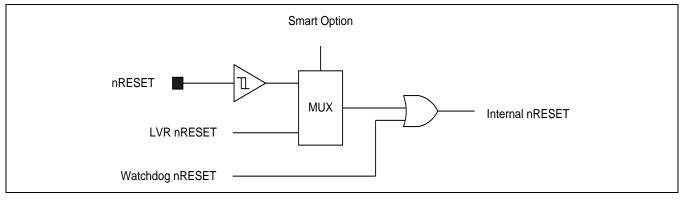

| •                          | Timing for S3F8S19A After RESET                                 | 8-3  |

| Figure 9-1                 | Port 0 Control Register High Byte (P0CONH)                      |      |

| -                          | Pull-Up Resistor Enable Register (P0PUR)                        |      |

| Figure 9-3                 | Port 0 Interrupt Control Register (P0INT)                       |      |

| Figure 9-4                 | Port 1 Control Register High Byte                               |      |

| Figure 9-5                 | Port 1 Control Register Low Byte                                |      |

| Figure 9-6                 | Port 2 High-Byte Control Register (P2CONH)                      |      |

| Figure 9-7                 | Port 2 Low-Byte Control Register (P2CONL)                       |      |

|                            | Port 3 High-Byte Control Register (P3CONH)                      |      |

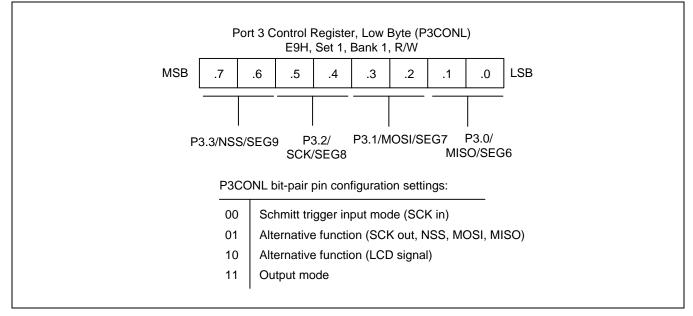

| Figure 9-9                 | Port 3 Low-Byte Control Register (P3CONL)                       | 9-11 |

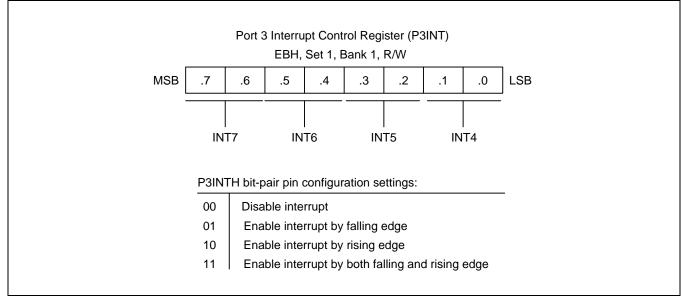

| Figure 9-10                | Port 3 Interrupt Control Register (P3INT)                       | 9-12 |

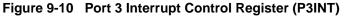

| Figure 9-11                | Port 3 and Port 0 Interrupt Pending Register (PINTPND)          | 9-12 |

|                            | Port 3 Pull-Up Resistor Enable Register (P3PUR)                 |      |

| Figure 9-13                | Port 3 N-Channel Open-Drain Mode Register (PNE3)                | 9-13 |

| Figure 9-14                | Port 4 High-Byte Control Register (P4CONH)                      | 9-15 |

| Figure 9-15                | Port 4 Low-Byte Control Register (P4CONL).                      | 9-15 |

| Figure 9-16                |                                                                 |      |

| Figure 9-17                | · · · · · · · · · · · · · · · · · · ·                           |      |

| Figure 10-1                |                                                                 |      |

| Figure 10-2                |                                                                 |      |

| Figure 11-1                |                                                                 | 11-2 |

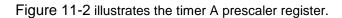

| Figure 11-2                |                                                                 | 11-3 |

| Figure 11-3                |                                                                 |      |

| Figure 12-1                | Stop Wake-Up Timer Control Register (SWTCON)                    |      |

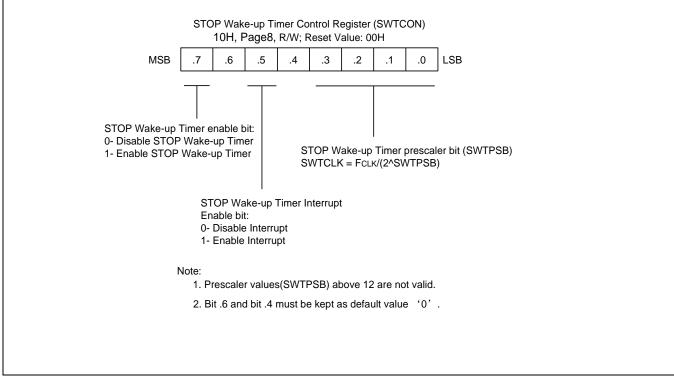

| Figure 12-2                |                                                                 |      |

| Figure 12-3                |                                                                 |      |

| Figure 12-3                |                                                                 |      |

| Figure 13-1<br>Figure 13-2 |                                                                 |      |

| •                          | Timer 0 Functional Block Diagram                                |      |

| <b>U</b>                   | Timer 1 Control Register (T1CON)                                |      |

| ingule 13-4                |                                                                 | 13-0 |

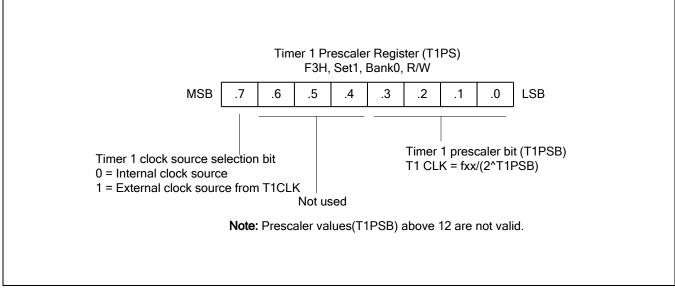

| Figure 13-5  | Timer 1 Prescaler Register (T1PS)                               |       |

|--------------|-----------------------------------------------------------------|-------|

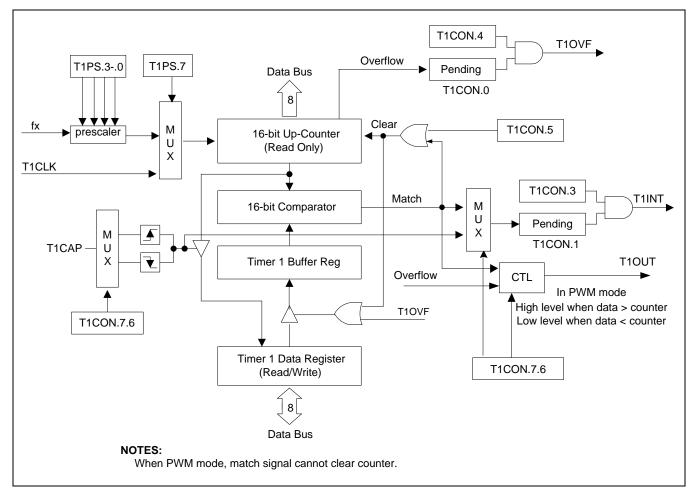

|              | Timer 1 Functional Block Diagram                                |       |

|              | Timer 2 Control Register (T2CON)                                |       |

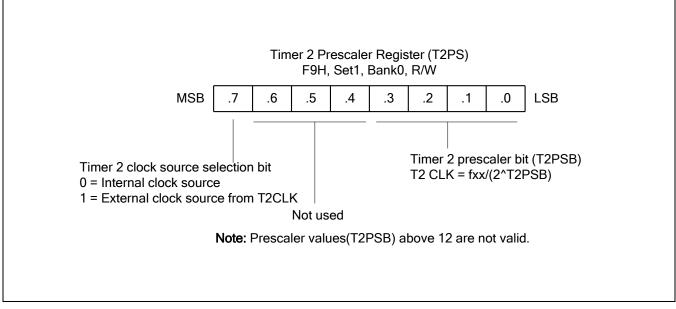

|              | Timer 2 Prescaler Register (T2PS)                               |       |

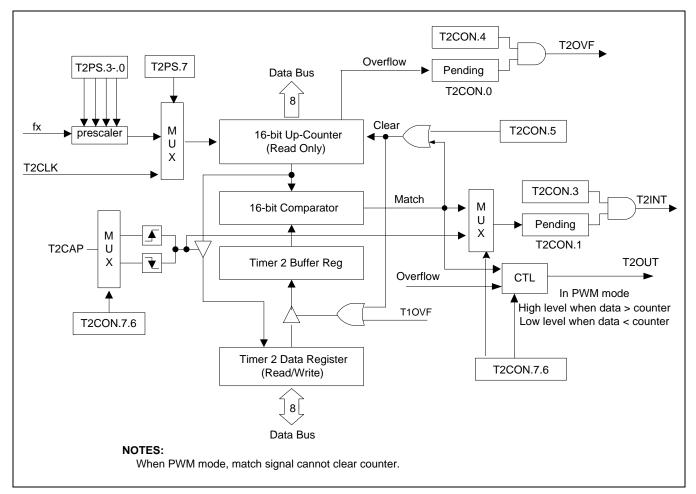

| Figure 13-9  | Timer 2 Functional Block Diagram                                | 13-16 |

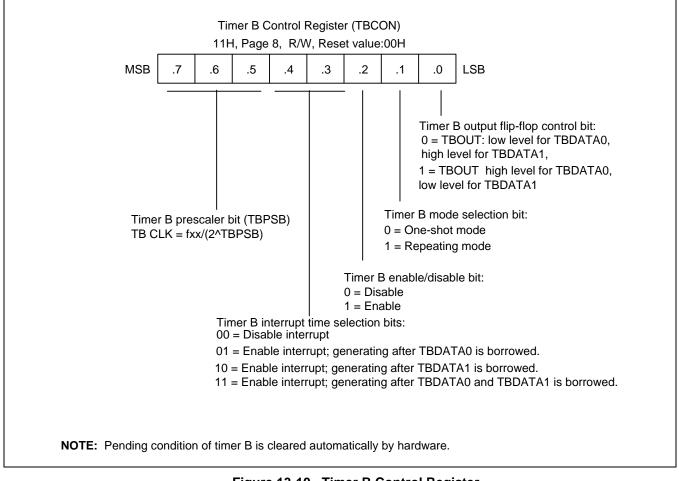

| Figure 13-10 | Timer B Control Register                                        | 13-17 |

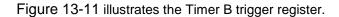

| Figure 13-11 | Timer B Trigger Register (TBTRG)                                | 13-18 |

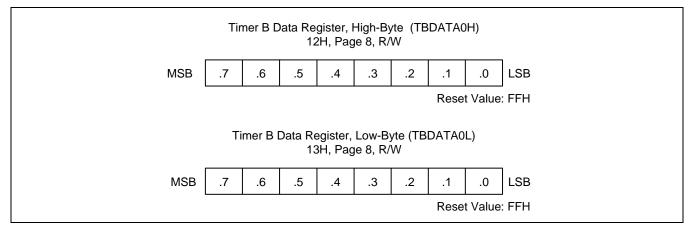

|              | Timer B Data Registers (TBDATA0H/L)                             |       |

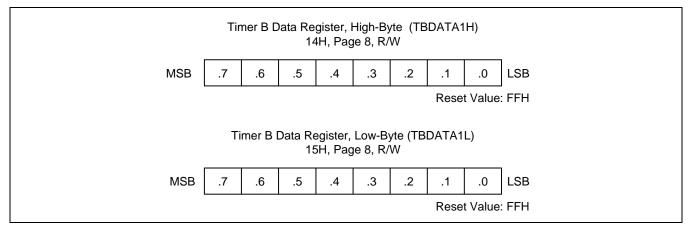

|              | Timer B Data Registers (TBDATA1H/L)                             |       |

|              | Timer B Functional Block Diagram                                |       |

|              | Timer B Output Flip-Flop Waveforms in Repeat Mode               |       |

|              | Watch Timer Control Register (WTCON)                            |       |

|              | Watch Timer Circuit Diagram                                     |       |

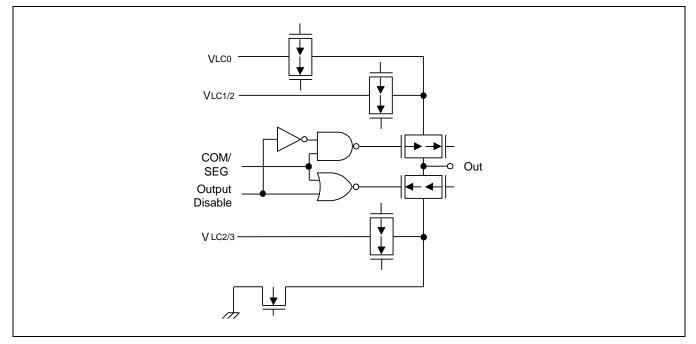

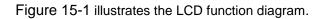

|              | LCD Function Diagram                                            |       |

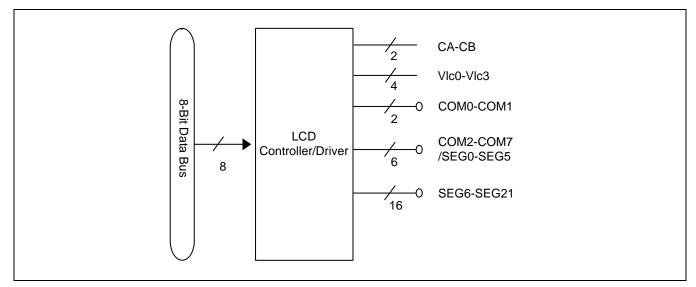

|              | LCD Circuit Diagram                                             |       |

|              | LCD Display Data RAM Organization                               |       |

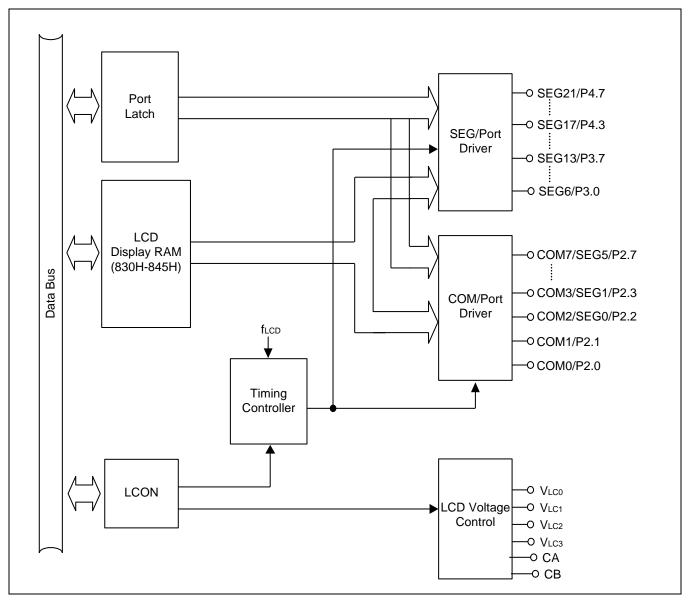

|              | LCD Control Register (LCON)                                     |       |

|              | LCD Mode Control Register (LMOD)                                |       |

|              | Internal Resistor Bias Pin Connection                           |       |

|              | External Resistor Bias Pin Connection                           |       |

| <b>Q</b>     | Capacitor Bias Pin Connection                                   |       |

|              |                                                                 |       |

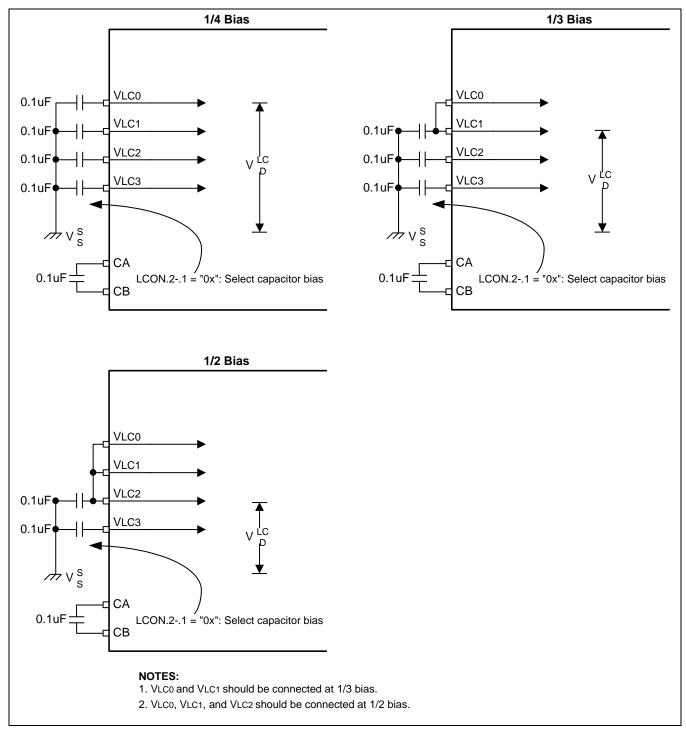

|              | Select/No-Select Signal in 1/2 Duty, 1/2 Bias Display Mode      |       |

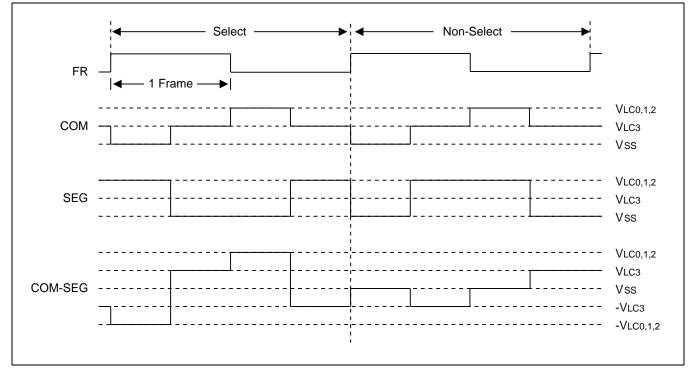

|              | Select/No-Select Signal in 1/3 Duty, 1/3 Bias Display Mode      |       |

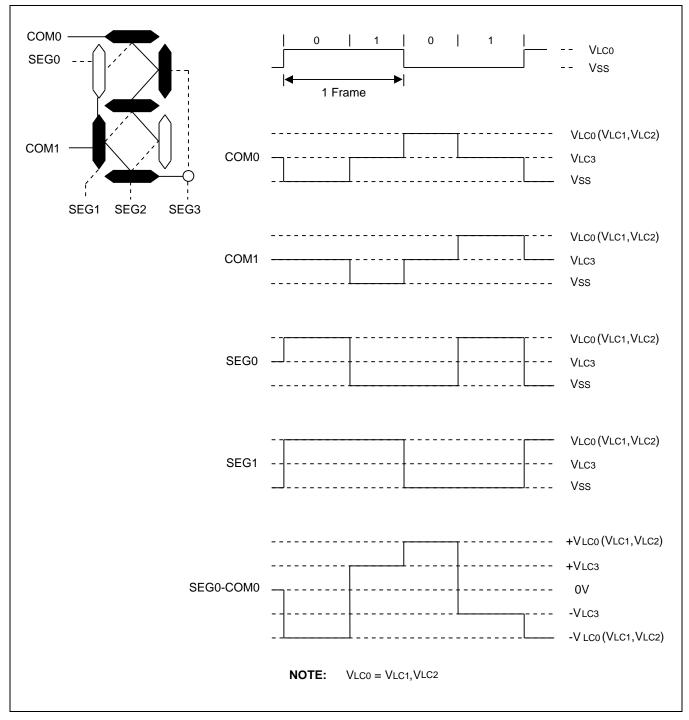

|              | LCD Signal Waveforms (1/2 Duty, 1/2 Bias)                       |       |

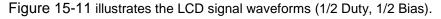

|              | LCD Signal Waveforms (1/3 Duty, 1/3 Bias)                       |       |

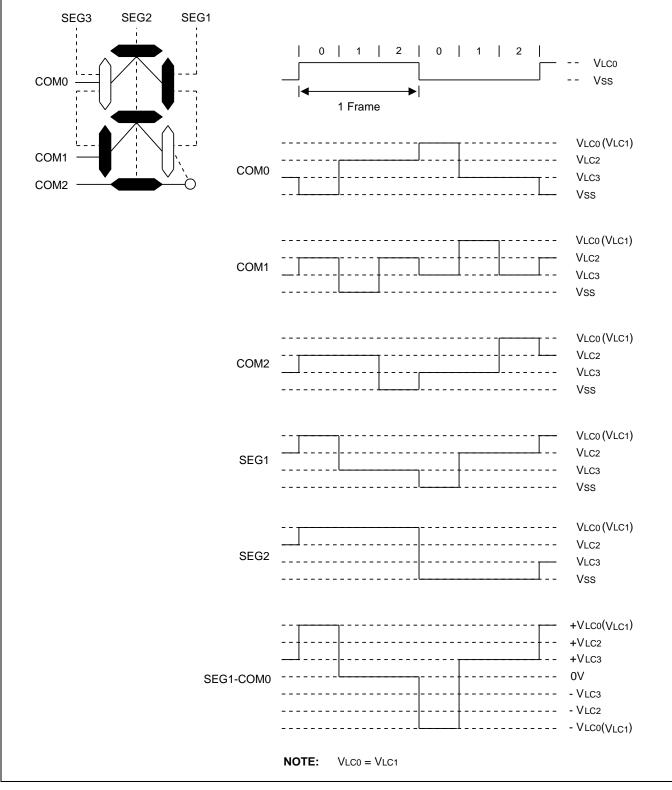

|              | LCD Signal Waveforms (1/4 Duty, 1/3 Bias)                       |       |

|              | LCD Signal Waveforms (1/8 Duty, 1/4 Bias)                       |       |

|              | A/D Converter Control Register (ADCON)                          |       |

| <b>Q</b>     | A/D Converter Circuit Diagram                                   |       |

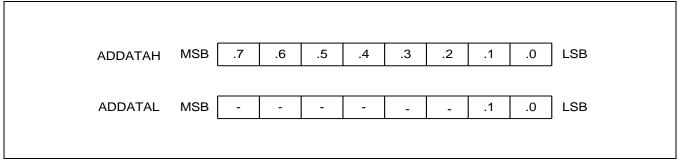

| Figure 16-3  | A/D Converter Data Register (ADDATAH/L)                         |       |

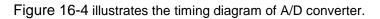

|              | A/D Converter Timing Diagram                                    |       |

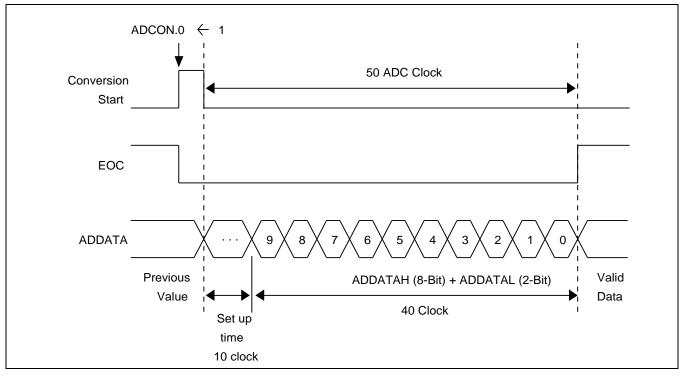

|              | Recommended A/D Converter Circuit for Highest Absolute Accuracy |       |

| <b>Q</b>     | SPI Block Diagram                                               |       |

|              | SPI Data Timing                                                 |       |

|              | SPI Control Register (SPICON)                                   |       |

|              | SPI Status Register (SPISTAT)                                   |       |

| •            | SPI Data Register (SPIDATA)                                     |       |

| Figure 18-1  | Multi-Master I2C Bus Control Register (ICCR)                    |       |

|              | Multi-Master I2C Bus Control/Status Register (ICSR)             |       |

| Figure 18-3  | Multi-Master I2C Bus Tx/Rx Data Shift Register (IDSR)           |       |

| Figure 18-4  | Multi-Master I2C Bus Address Register (IAR)                     |       |

|              | I2C Bus Block Diagram                                           |       |

| Figure 18-6  |                                                                 |       |

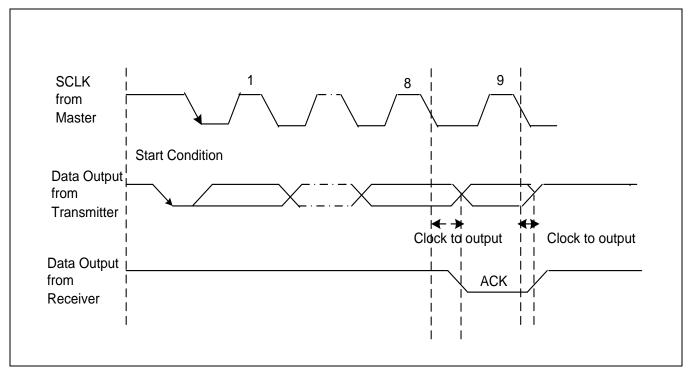

| Figure 18-7  | Input Data Protocol                                             |       |

| Figure 18-8  | Interrupt Pending Information                                   |       |

|              | I2C Bus Interface Data Formats                                  |       |

| •            | Acknowledge Response from Receiver                              |       |

| Figure 18-11 |                                                                 |       |

|              | Read Operation Sequence                                         |       |

|              | UART 0 High Byte Control Register (UART0CONH)                   |       |

|              | UART 0 Low Byte Control Register (UART0CONL)                    |       |

| Figure 19-3  | UART 0 Data Register (UDATA0)                                   |       |

| Figure 10.4 LIAPT 0 Paud Pate Date Pagister (PPDATA0)                                                                  | 10 5 |

|------------------------------------------------------------------------------------------------------------------------|------|

| Figure 19-4 UART 0 Baud Rate Data Register (BRDATA0)<br>Figure 19-5 UART 0 Functional Block Diagram                    |      |

| Figure 19-5 OART 0 Functional Block Diagram                                                                            |      |

| Figure 19-7 Timing Diagram for Serial Port Mode 1 Operation                                                            |      |

| Figure 19-8 Timing Diagram for Serial Port Mode 2 Operation                                                            |      |

| Figure 19-9 Timing Diagram for Serial Port Mode 3 Operation                                                            |      |

| Figure 19-10 Connection Example for Multiprocessor Serial Data Communications                                          |      |

| Figure 20-1 UART 1 High Byte Control Register (UART1CONH)                                                              |      |

| Figure 20-2 UART 1 Low Byte Control Register (UART1CONL)                                                               |      |

| Figure 20-3 UART 1 Data Register (UDATA1)                                                                              |      |

| Figure 20-4 UART 1 Baud Rate Data Register (BRDATA1)                                                                   |      |

| Figure 20-5 UART 1 Functional Block Diagram                                                                            |      |

| Figure 20-6 Timing Diagram for Serial Port Mode 0 Operation                                                            |      |

| Figure 20-7 Timing Diagram for Serial Port Mode 1 Operation                                                            |      |

| Figure 20-8 Timing Diagram for Serial Port Mode 2 Operation                                                            |      |

| Figure 20-9 Timing Diagram for Serial Port Mode 3 Operation                                                            |      |

| Figure 20-10 Connection Example for Multiprocessor Serial Data Communications                                          |      |

| Figure 21-1 Flash Memory Control Register (FMCON)                                                                      |      |

| Figure 21-2 Flash Memory User Programming Enable Register (FMUSR)                                                      | 21-4 |

| Figure 21-3 Flash Memory Sector Address Register High Byte (FMSECH)                                                    |      |

| Figure 21-4 Flash Memory Sector Address Register Low Byte (FMSECL)                                                     |      |

| Figure 21-5 Program Memory Address Space                                                                               |      |

| Figure 21-6 Sector Configurations in User Program Mode                                                                 |      |

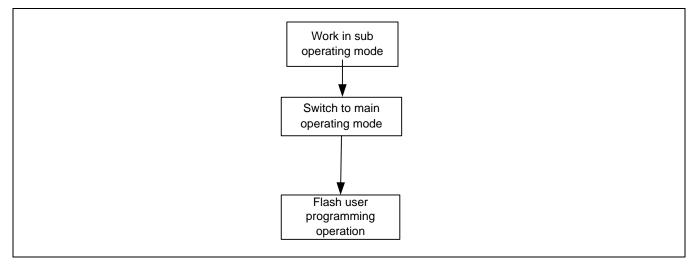

| Figure 21-7 Flash Operation Sequence in Sub Operating Mode                                                             |      |

| Figure 22-1 Low Voltage Reset Circuit                                                                                  |      |

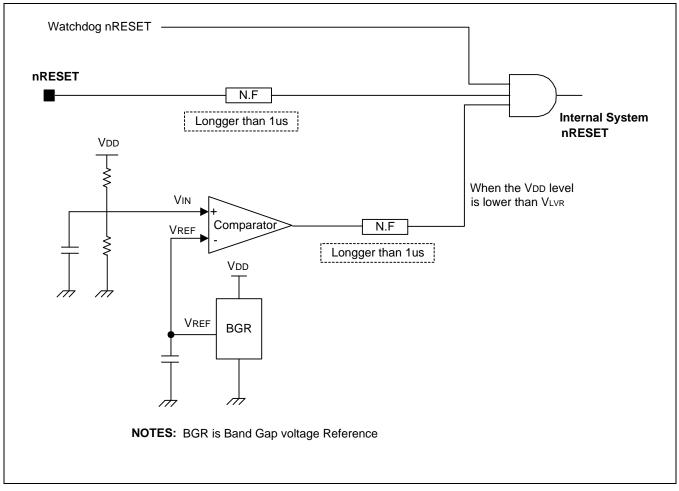

| Figure 22-2 Low Voltage Detect (LVD) Block Diagram                                                                     |      |

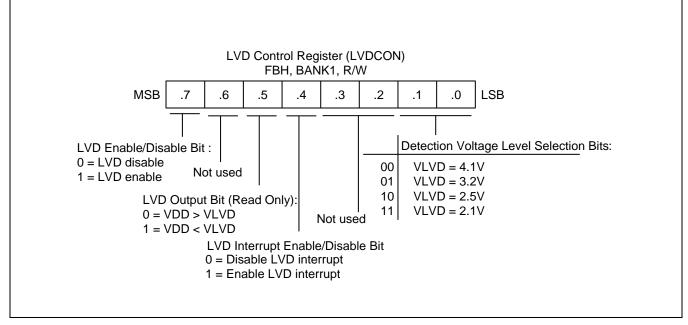

| Figure 22-3 Flash Low Voltage Detect Control Register (LVDCON)                                                         |      |

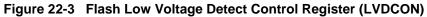

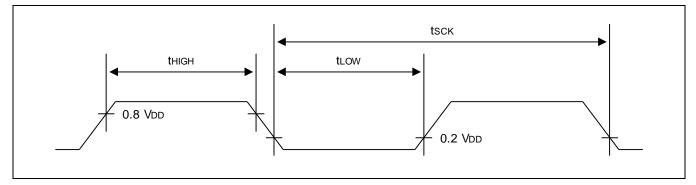

| Figure 23-1 Input Timing Measurement Points                                                                            |      |

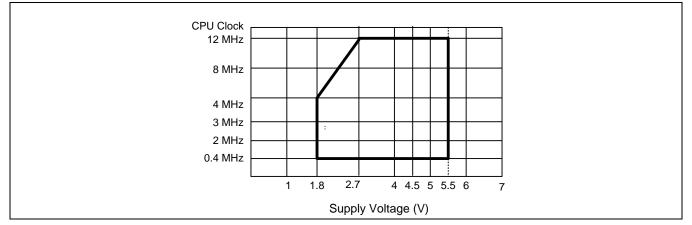

| Figure 23-2 Operating Voltage Range                                                                                    |      |

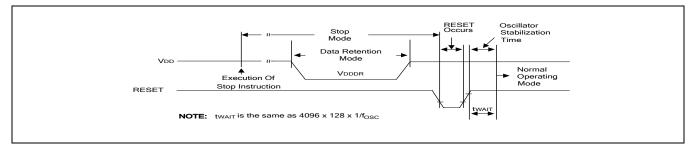

| Figure 23-3 Stop Mode Release Timing When Initiated by a RESET<br>Figure 23-4 Waveform for UART Timing Characteristics |      |

| Figure 23-5 LVR Reset Timing                                                                                           |      |

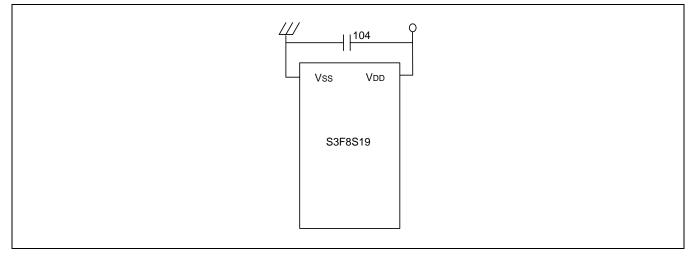

| Figure 23-6 The Circuit Diagram to Improve EFT Characteristics                                                         |      |

| Figure 24-1 48-QFP-1010E Package Dimensions                                                                            |      |

| Figure 25-1 S3F8S19A Pin Assignments (48-QFP-1010E)                                                                    |      |

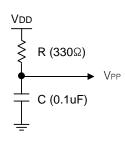

| Figure 25-2 RC Delay Circuit                                                                                           |      |

| Figure 25-3 PCB Design Guide for on Board Programming                                                                  |      |

| Figure 26-1 Development System Configuration                                                                           |      |

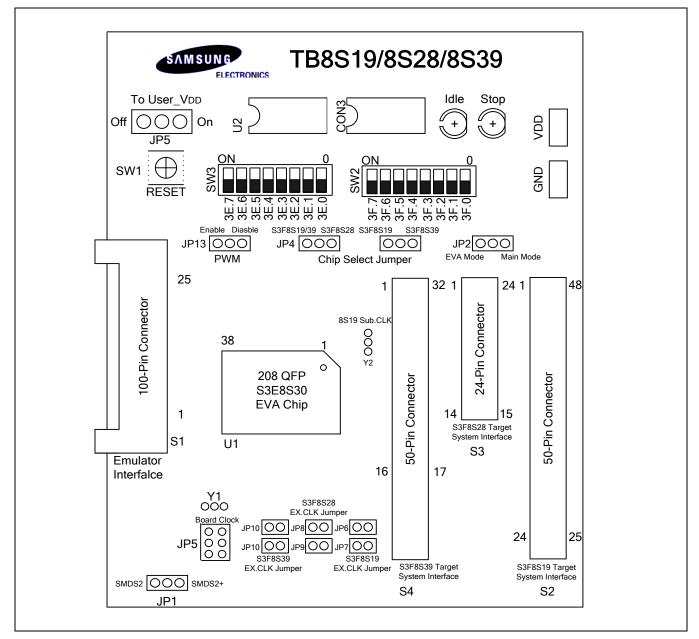

| Figure 26-2 TB8S19/8S28/8S39 Target Board Configuration                                                                |      |

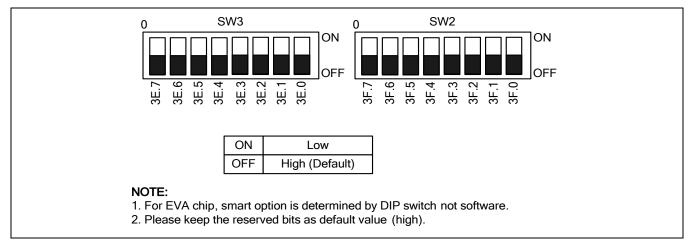

| Figure 26-3 DIP Switch for Smart Option                                                                                |      |

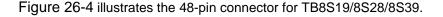

| Figure 26-4 48-Pin Connector for TB8S19/8S28/8S39                                                                      |      |

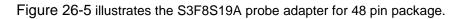

| Figure 26-5 S3F8S19A Probe Adapter for 48 Pin Package                                                                  |      |

|                                                                                                                        |      |

# **List of Tables**

#### Table Number

Title

## Page Number

| Table 1-1   | Pin Descriptions of 48-QFP                           | 1-8  |

|-------------|------------------------------------------------------|------|

| Table 2-1   | S3F8S19A Register Type Summary                       |      |

| Table 4-1   | System and Peripheral Control Registers Set 1        | 4-2  |

| Table 4-2   | System and Peripheral Control Registers Set 1 Bank 0 | 4-3  |

| Table 4-3   | System and Peripheral Control Registers Set 1 Bank 1 |      |

| Table 4-4   | System and Peripheral Control Registers Page 8       |      |

| Table 5-1   | Interrupt Control Register Overview                  |      |

| Table 5-2   | Interrupt Source Control and Data Registers          |      |

| Table 6-1   | Instruction Group Summary                            |      |

| Table 6-2   | Flag Notation Conventions                            |      |

| Table 6-3   | Instruction Set Symbols                              |      |

| Table 6-4   | Instruction Notation Conventions                     | 6-8  |

| Table 6-5   | Opcode Quick Reference (0–7)                         | 6-9  |

| Table 6-6   | Opcode Quick Reference (8–F)                         | 6-10 |

| Table 6-7   | Condition Codes                                      |      |

| Table 8-1   | S3F8S19A Set1 Register Values after RESET            |      |

| Table 8-2   | System and Peripheral Control Registers Set1 Bank 0  |      |

| Table 8-3   | System and Peripheral Control Registers Set1 Bank 1  |      |

| Table 8-4   | System and Peripheral Control Registers Page 8       |      |

| Table 9-1   | S3F8S19A Port Configuration Overview                 |      |

| Table 9-2   | Port Data Register Summary                           |      |

| Table 12-1  |                                                      |      |

| Table 17-1  | 5                                                    |      |

| Table 17-2  |                                                      |      |

| Table 18-1  |                                                      |      |

| Table 19-1  | , , , , , , , , , , , , , , , , , , ,                |      |

| Table 20-1  | , , , , , , , , , , , , , , , , , , ,                |      |

| Table 21-1  |                                                      |      |

| Table 21-2  |                                                      |      |

| Table 23-1  | 5                                                    |      |

| Table 23-2  |                                                      |      |

|             | AC Electrical Characteristics                        |      |

|             | Oscillator Characteristics                           |      |

|             | Oscillation Stabilization Time                       |      |

|             | Data Retention Supply Voltage in Stop Mode           |      |

| Table 23-7  |                                                      |      |

| Table 23-8  | I                                                    |      |

| Table 23-9  | 6                                                    |      |

| Table 23-1  |                                                      |      |

| Table 23-1  |                                                      |      |

| Table 23-1  |                                                      |      |

| I able 23-1 | 3 LVR Circuit Characteristics                        |      |

| Table 25-1 | Descriptions of Pins Used to Read/Write the Flash in Tool Program mode  |  |

|------------|-------------------------------------------------------------------------|--|

| Table 25-2 | Reference Table for Connection                                          |  |

| Table 26-1 | UART 1 Low Byte Control Register (UART1CONL)                            |  |

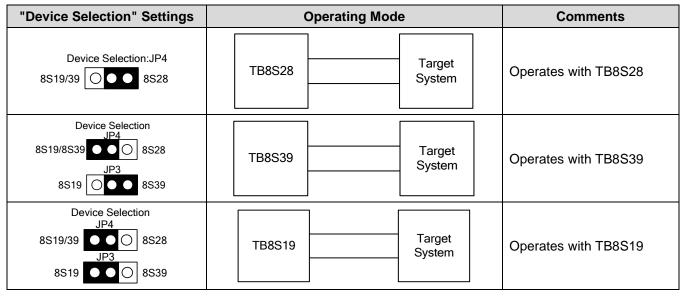

| Table 26-2 | Device Selection Settings for TB8S19/8S28/8S39                          |  |

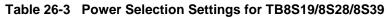

| Table 26-3 | Power Selection Settings for TB8S19/8S28/8S39                           |  |

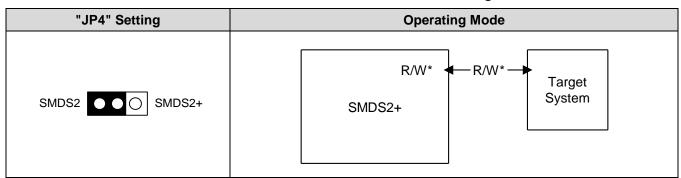

| Table 26-4 | The SMDS2+ Tool Selection Setting                                       |  |

| Table 26-5 | Using Single Header Pins to Select Clock Source/PWM/Operation Mode      |  |

| Table 26-6 | Using Single Header Pins as the Input Path for External Trigger Sources |  |

# List of Examples

#### Example Number

Title

#### Page Number

| Example 2-1  | Setting the Register Pointers                               |     |

|--------------|-------------------------------------------------------------|-----|

| Example 2-2  | Using the RPs to Calculate the Sum of a Series of Registers |     |

| Example 2-3  | Addressing the Common Working Register Area                 |     |

| Example 2-4  | Standard Stack Operations Using PUSH and POP                |     |

| Example 7-1  | Switching the CPU clock                                     | 7-7 |

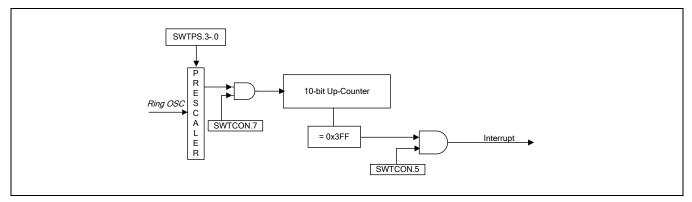

| Example 12-1 | Using Stop Wake-Up Timer                                    |     |

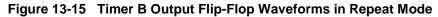

| Example 13-1 | To Generate 38 kHz, 1/3 Duty Signal through P2.1            |     |

| Example 13-2 | To generate a one pulse signal through P2.1                 |     |

| Example 15-1 | LCD Display on, After Capacitor Bias Selected               |     |

|              | Configuring A/D Converter                                   |     |

|              | Sector Erase                                                |     |

| Example 21-2 | Program                                                     |     |

|              | Reading                                                     |     |

| •            | Hard Lock Protection                                        |     |

|              |                                                             |     |

# Product Overview

# 1.1 S3C8 Series Microcontrollers

SAM8RC family of Zilog of 8-bit single-chip Complementary Metal Oxide Semiconductor (CMOS) microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-programmable ROM sizes. Address/data bus architecture and a large number of bit-configurable Input/Output (I/O) ports provide a flexible programming environment for applications with varied memory and I/O requirements. It includes timer/counters with selectable operating modes to support real-time operations.

# 1.2 S3F8S19A Microcontroller

It fabricates the S3F8S19A single-chip CMOS microcontrollers by using the highly advanced CMOS process technology based on the latest CPU architecture of Zilog.

The S3F8S19A is a microcontroller with an embedded 32 KB full-Flash ROM.

By using a proven modular design approach, Zilog engineers have successfully developed the S3F8S19A by integrating these peripheral modules with the powerful SAM8 RC core:

- Five configurable I/O ports (40 pin)

- Twenty-six interrupt sources and eight interrupt levels

- Eight bit-programmable pins for external interrupts

- One stop wake up timer function

- One 8-bit basic timer for oscillation stabilization

- One 8-bit timer/counter and Four 16-bit timer/counters with selectable operating modes

- Watch timer for real time

- LCD Controller/driver

- Two asynchronous UART modules

- One Serial Peripheral Interface (SPI) module

- One Inter Integrated Circuit (I2C) module

- Analog to digital converter with 10 input channels and 10-bit resolution

- One Buzzer (BUZ) for programmable frequency output

The S3F8S19A microcontroller is ideal for use in a wide range of home applications that require simple timer/counter, Analog-to-Digital Converter (ADC), LCD, etc. They are currently available in a 48-pin QFP package.

| Comparison         | S3F8S19A |

|--------------------|----------|

| Flash Size (Bytes) | 32K      |

## 1.3 Features

#### 1.3.1 CPU

• SAM88RC CPU core

#### 1.3.2 Memory

Features of internal multi-time program Full-Flash memory are:

- 32K × 8 bits program memory (S3F8S19A)

- o Sector size: 128 bytes

- User programmable by "LDC" instruction

- Sector erase available

- o Fast programming time

- External serial programming support

- Endurance: 10,000 erase/program cycles

- o 10 years data retention

- Data Memory (RAM)

- Including LCD display data memory

- 2,086 × 8 bits data memory

#### 1.3.3 Instruction Set

- 78 instructions

- Idle and Stop instructions

#### 1.3.4 I/O Pins

• 40 normal I/O pins in the 48-pin QFP package

#### 1.3.5 Interrupts

- 8 interrupt levels and 26 interrupt sources

- Fast interrupt processing feature

#### 1.3.6 Timers and Timer/Counters

- One programmable 8-bit basic timer (BT) for oscillation stabilization control or watchdog timer function.

- One 8-bit timer/counter (Timer A) with three operating modes:

- Interval mode

- Capture mode

- Pulse Width Modulation (PWM) Mode

- One 16-bit timer/counter (Timer 0) with Interval mode and PWM mode

- Two 16-bit timer/counter (Timer 1/2) with three operating modes:

- Interval mode

- Capture mode

- PWM mode

- One 16-bit timer/counter (Timer B) with one-shot pulse mode and repeating output mode. It can be triggered by external input or software.